# A plug-and-play real-time architecture for MPSoC-FPGAs targeting interventional Computed Tomography

Dissertation zur Erlangung des akademischen Grades

# Doktoringenieur

# (Dr.-Ing.)

von M. Sc. Daniele Passaretti geb. am 23. Mai 1992 in Gaeta (Italien) genehmigt durch die Fakultät für Elektrotechnik und Informationstechnik der Otto-von-Guericke Universität Magdeburg Gutachter: Prof. Dr.-Ing. Thilo Pionteck Prof. Dr. rer. nat. Nicola D'Ascenzo

Promotionskolloquium am 10. September 2024

Daniele Passaretti: A plug-and-play real-time architecture for MPSoC-FPGAs targeting interventional Computed Tomography, Copyright © 2024

#### Abstract

In recent years, new image-guided interventional procedures, such as interventional Computed Tomography (iCT), have been explored to tackle the increasing number of tumors. During these interventional procedures, surgeons track the needle used for tumor ablation within the patient's body with the support of Computed Tomography (CT) or multimodal CT/Positron Emission Tomography (PET)/Magnetic Resonance Imaging (MRI) techniques. While CT scanners for tumor diagnosis have been typically designed as custom closed systems, new scanners for interventional procedures aim to be adaptable and configurable for multimodality scanning, providing real-time images. Therefore, from the system designer perspective, these scanners are considered Cyber-Physical System (CPS) devices, where components must be controlled, and data must be acquired and processed in real time.

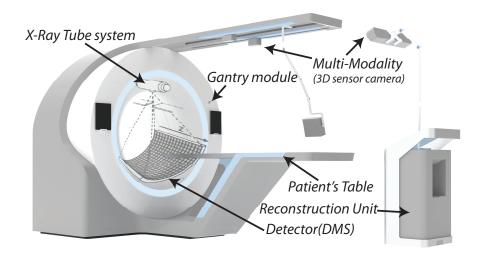

The "Konfigurierbarer, Interfaceoffener, Dosissparender Computertomograph" (KIDS-CT) scanner is the first open-interface CT scanner assembled by Academia aiming to provide new features: extension for adding new components in a plug-and-play fashion, and user-accessible sensor/actuator parameters (e.g., individual settings of detector, X-ray tube voltage, Time-of-flight cameras). These features allow researchers and/or physicians to explore new multimodality techniques and interventional procedures with the aim of optimizing the X-ray dose and enhancing reconstruction algorithms.

This thesis addresses the problem of real-time data acquisition and processing in CPSs and their extension capabilities for adding components in a plug-and-play fashion. It focuses on the KIDS-CT scanner, for which multimodality functionalities and real-time support must be provided in order to conduct and explore iCT procedures. To address these problems at the system and hardware design level, this research work firstly contributes in the design process of the CT scanner, modeled as a CPS device, by proposing a System Architecture and the associated Communication Infrastructure; Secondly, it proposes a new Control-Data Acquisition System (CDAS) architecture for Multi-Processor System-on-Chip Field Programmable Gate-Array (MPSoC-FPGA) platforms. Although the proposed work has been implemented and validated targeting the KIDS-CT scanner, it is configurable for various CPS applications where data must be collected and processed on the fly, while components must be controlled in real time. In fact, the CDAS plays a crucial role in controlling CPS components at the device level, collecting and processing data in real time, and providing plug-and-play capability for the target application, such as the KIDS-CT scanner.

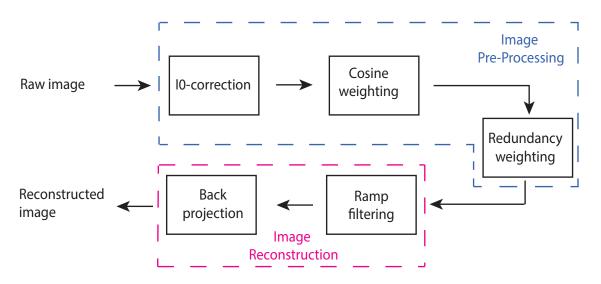

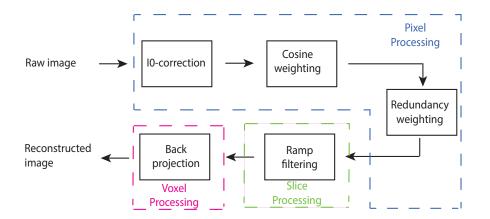

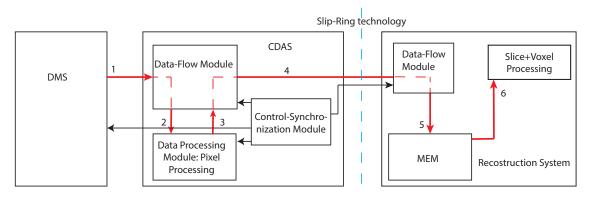

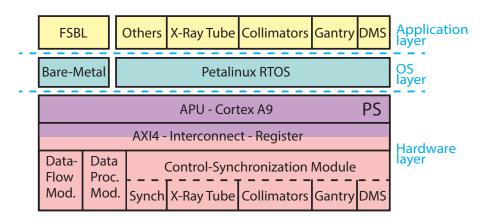

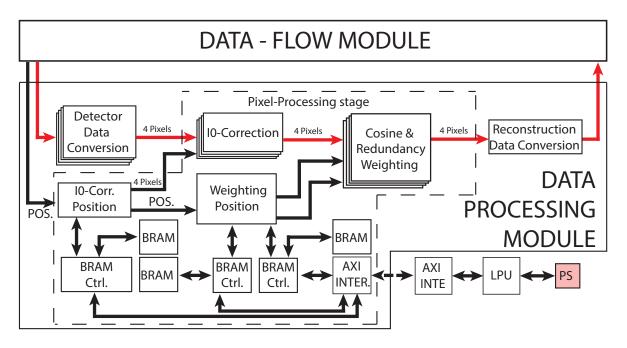

In order to reach these aims, various methodologies have been proposed: Real-time and non-real-time tasks are properly mapped between the Programmable Logic and the Processing System of the MPSoC-FPGA; The Communication Infrastructure has been modeled in layers and classes that contain different protocols on the base of the task type; A dataflow-module and a data-processing module have been proposed to collect, and preprocess data on the fly, without using external memory. In addition, data can be pre-processed in different formats, making it suitable for exploring the design space by tuning data formats to determine the most appropriate design configuration to pre-process data for interventional procedures.

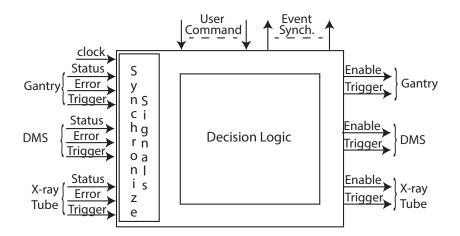

As part of this work, a guideline for designing an open-interface CT scanner has been provided at the system level and digital signal processing level. The proposed communication protocols for the plug-and-play capability and the real-time support have been described. Furthermore, the hardware/software CDAS architecture has been described through its three main components: the Control-synchronization Module, the Data-flow Module, and the Data-processing Module. Moreover, a novel hardware isolation method to enable isolation support on MPSoC-FPGAs has been proposed; the proposed isolation method solves the problem of isolation between hardware modules inside the MPSoC-FPGA.

Finally, this work describes the realization of the System Architecture, the Communication Infrastructure and the CDAS architecture in the specific case of the KIDS-CT scanner. For this purpose, the XC7Z045 MPSoC-FPGA has been used for implementing the CDAS architecture. Here, the proposed optimizations have permitted to achieve an efficient solution, which use only 7.81% of Look-Up Tables, 5.82% of Flip-Flops, 5% of Digital Signal Processors, and 7.89% of Block RAMs, and collect and process pixel data in an estimated time of 467.8 ns. Since pixel data are processed on the fly during the acquisition of each projection, and this processing is faster than the "integration period" required to acquire a projection, the proposed pre-processing solution adds zero latency to the acquisition time. Therefore, the Graphics Processing Unit (GPU) on the reconstruction system only needs to perform the rest of the processing, resulting the entire acquisition and reconstruction time much faster than before. Such a solution could not be achieved with the standard approach, as it would exceed the capacity of the available Digital Signal Processors in the selected MPSoC-FPGA. Furthermore, the proposed optimized solution is 6.4 times faster than the standard approach. In conclusion, this thesis answers to the problem of how to provide real-time support and plug-and-play capability within complex CPSs such as the KIDS-CT scanner, and enables this scanner to explore new multimodality techniques and interventional procedures.

## Zusammenfassung

Um die zunehmende Zahl von Tumorerkrankungen zu bekämpfen, wurden in den letzten Jahren neue bildgesteuerte interventionelle Methoden erforscht, wie z. B. das Interventional Computed Tomography (iCT)-Verfahren. Bei diesen interventionellen Verfahren verfolgen die Chirurgen die bei der Tumorentfernung verwendete Nadel im Körper des Patienten mit Computed Tomography (CT) oder multimodalen CT/Positron Emission Tomography (PET)/Magnetic Resonance Imaging (MRI)-Techniken. Während diagnostische CT-Scanner in der Regel als zugeschnittene, geschlossene Systeme konzipiert werden, sollen neue Scanner für interventionelle Verfahren anpassungsfähig und für multimodales Scannen konfigurierbar sein sowie Echtzeitbilder liefern. Daher funktionieren diese Scanner auf der Ebene des Systemdesigns als Cyber-Physical System (CPS)-Geräte, bei denen die Komponenten gesteuert und die Daten in Echtzeit erfasst und verarbeitet werden müssen.

Der "Konfigurierbare, Interfaceoffene, Dosissparende Computertomograph" (KIDS-CT)-Scanner ist der erste von der akademischen Welt fertiggestellte CT-Scanner mit offener Schnittstelle, der neue Funktionen bietet: Erweiterungen für das Hinzufügen neuer Komponenten im Plug-and-Play-Verfahren und für den Benutzer zugängliche Sensor/Aktor-Parameter (z. B. individuelle Einstellungen des Detektors, der Spannung der Röntgenröhre und der Time-of-Flight-Kameras). Diese Funktionen ermöglichen es Forschenden und/oder Ärzten, neue multimodale Techniken und interventionelle Verfahren mit dem Ziel zu erforschen, die Röntgendosis zu optimieren und die Rekonstruktionsalgorithmen zu verbessern.

Diese Arbeit befasst sich mit der Problematik der Echtzeit-Datenerfassung und -Verarbeitung innerhalb von CPSs und deren Erweiterungsmöglichkeiten für das Hinzufügen von Komponenten in Plug-and-Play-Weise. Der Fokus liegt auf dem KIDS-CT-Scanner, für den multimodale Funktionalitäten und Echtzeitunterstützung bereitgestellt werden müssen, um iCT-Verfahren durchzuführen und zu erforschen. Um diese Probleme auf der System- und Hardware-Entwurfsebene anzugehen, trägt diese Forschungsarbeit erstens zum Entwurfsprozess des als CPS-Gerät modellierten CT-Scanners bei, indem sie eine Systemarchitektur und die zugehörige Kommunikationsinfrastruktur vorschlägt; zweitens schlägt sie eine neue Control-Data Acquisition System (CDAS)-Architektur für Multi-Processor System-on-Chip Field Programmable Gate-Array (MPSoC-FPGA)-Plattformen vor. Obwohl die Arbeit für den KIDS-CT-Scanner implementiert und validiert wurde, ist sie für verschiedene CPS-Anwendungen konfigurierbar, die unter Verwendung der entwickelten Systemarchitektur entwickelt werden können. Tatsächlich spielt das CDAS eine entscheidende Rolle bei der Steuerung von CPS-Komponenten auf Geräteebene, bei der Erfassung und Verarbeitung von Daten in Echtzeit und bei der Bereitstellung von Plug-and-Play-Fähigkeiten für die Zielanwendung, wie z. B. den KIDS-CT-Scanner.

Um diese Ziele zu erreichen, werden verschiedene Methoden angewandt: Echtzeit- und Nicht-Echtzeit-Aufgaben werden auf geeignete Art und Weise zwischen der programmierbaren Logik und dem Verarbeitungssystem des MPSoC-FPGA abgebildet; die Kommunikationsinfrastruktur wird in Ebenen und Klassen modelliert, die verschiedene Protokolle auf der Grundlage des Aufgabentyps enthalten; ein Datenflussmodul und ein Datenverarbeitungsmodul werden implementiert, um Daten zu sammeln und vorzubehandeln, ohne externen Speicher zu verwenden. Darüber hinaus kann das Datenverarbeitungsmodul Daten in verschiedenen Formaten vorverarbeiten.

Diese Flexibilität ermöglicht die Erkundung des Designraums durch Anpassung der Datenformate. Eine solche Abstimmung hilft bei der Bestimmung der am besten geeigneten Designkonfiguration für die Vorverarbeitung von Daten bei interventionellen Verfahren.

Im Rahmen dieser Arbeit wird ferner ein Leitfaden für die Entwicklung eines CT-Scanners mit offener Schnittstelle auf Systemebene und auf Ebene der digitalen Signalverarbeitung bereitgestellt. Die integrierten Kommunikationsprotokolle für die Plug-and-Play Fähigkeit und die Echtzeitunterstützung werden beschrieben. Darüber hinaus wird die Software-/Hardware-Architektur von CDAS mit ihren drei Hauptkomponenten beschrieben: das Steuerungs-/Synchronisationsmodul, das Datenflussmodul und das Datenverarbeitungsmodul. Darüber hinaus wurde eine neuartige Hardware-Isolationsmethode entwickelt, um die Isolationsunterstützung auf MPSoC-FPGAs zu ermöglichen; die dazugehörige Isolationsmethode löst das Problem der Isolation zwischen Hardware-Modulen innerhalb des MPSoC-FPGA.

Insgesamt beschreibt diese Arbeit die Realisierung der Systemarchitektur, der Kommunikationsinfrastruktur und der CDAS-Architektur im speziellen Fall des KIDS-CT -Scanners. Zu diesem Zweck wurde der XC7Z045 MPSoC-FPGA für die Implementierung der CDAS-Architektur verwendet. Mit den hier implementierten Optimierungen wurde eine effiziente Lösung erreicht, die nur 7,81% der Look-Up Tables, 5,82% der Flip-Flops, 5% der Digitalen Signalprozessoren und 7,89% der Block RAMs verwendet und Pixeldaten in einer geschätzten Zeit von 467,8 ns erfasst und verarbeitet. Da die Pixeldaten während der Erfassung jeder Projektion "on-the-fly" verarbeitet werden und diese Verarbeitung schneller ist als die für die Erfassung einer Projektion erforderliche Integrationszeit, fügt die vorgestellte Vorverarbeitungslösung der Erfassungszeit keine Latenz hinzu. Daher muss die Graphics Processing Unit (GPU) auf dem Rekonstruktionssystem nur den Rest der Verarbeitung durchführen, wodurch die gesamte Erfassungs- und Rekonstruktionszeit deutlich schneller ist als bei bisherigen Lösungen. Eine solche Lösung könnte mit dem Standardansatz nicht erreicht werden, da sie die Kapazität des verfügbaren Digitalen Signalprozessoren in dem ausgewählten MPSoC-FPGA übersteigen würde. Außerdem ist die vorgeschlagene optimierte Lösung 6,4-Mal schneller als der Standardansatz. Zusammenfassend wird die Frage beantwortet, wie Echtzeit-Unterstützung und Plug-and-Play-Fähigkeit innerhalb komplexer CPSs, wie dem KIDS-CT-Scanner, bereitgestellt und wie damit neue multimodale Techniken und interventionelle Verfahren erforscht werden können.

# **Publications**

# **Publication As First Author**

#### Original works in peer-reviewed international journals

- [DP 1] D. Passaretti, M. Ghosh, S. Abdurahman, M. L. Egito, and T. Pionteck. "Hardware Optimizations of the X-ray Pre-Processing for Interventional Computed Tomography Using the FPGA". In: Applied Sciences 12.11 (2022). ISSN: 2076-3417. DOI: 10.3390/app12115659. URL: https://www.mdpi.com/2076-3417/12/11/ 5659.

- [DP 2] D. Passaretti, M. Steiger, and T. Pionteck. "Enabling Plug-and-Play in Cyber-Physical Systems Using MPSoC-FPGAs". In: *IEEE Access* 11 (2023), pp. 116219– 116234. DOI: 10.1109/ACCESS.2023.3325742.

#### Original works in peer-reviewed international conferences

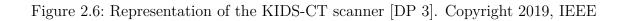

- [DP 3] D. Passaretti, J. M. Joseph, and T. Pionteck. "Survey on FPGAs in Medical Radiology Applications: Challenges, Architectures and Programming Models". In: 2019 International Conference on Field-Programmable Technology (ICFPT). 2019, pp. 279–282. DOI: 10.1109/ICFPT47387.2019.00047.

- [DP 4] D. Passaretti and T. Pionteck. "Hardware/Software Co-Design of a control and data acquisition system for Computed Tomography". In: 2020 9th International Conference on Modern Circuits and Systems Technologies (MOCAST). 2020, pp. 1–4. DOI: 10.1109/M0CAST49295.2020.9200273.

- [DP 5] D. Passaretti and T. Pionteck. "Configurable Pipelined Datapath for Data Acquisition in Interventional Computed Tomography". In: 2021 IEEE 29th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). 2021, pp. 257–257. DOI: 10.1109/FCCM51124.2021.00044.

- [DP 6] D. Passaretti, F. Boehm, M. Wilhelm, and T. Pionteck. "Hardware Isolation Support for Low-Cost SoC-FPGAs". In: Architecture of Computing Systems. Ed. by M. Schulz, C. Trinitis, N. Papadopoulou, and T. Pionteck. Cham: Springer International Publishing, 2022, pp. 148–163. ISBN: 978-3-031-21867-5.

[DP 7] D. Passaretti and T. Pionteck. "A Control Data Acquisition System Architecture for MPSoC-FPGAs in Computed Tomography". In: Applied Reconfigurable Computing. Architectures, Tools, and Applications. Ed. by F. Palumbo, G. Keramidas, N. Voros, and P. C. Diniz. Cham: Springer Nature Switzerland, 2023, pp. 361–365. ISBN: 978-3-031-42921-7.

# Patent

[DP 8] T. Hoffmann, D. Passaretti, R. Frysch, T. Pfeiffer, and G. Rose. MEDI-CAL IMAGING SYSTEM AND COMPUTER PROGRAM. US Patent US 2023/0377720 A1 (Pub. Date: Nov. 23, 2023), EP EP4225148A1 (Pub. Date: Aug. 16, 2023), JP2023544700A (Pub. Date: Oct. 25, 2023), WO2022073958A1 (Pub. Date: Apr. 14, 2022). Assignee: Otto-von-Guericke-Universität Magdeburg, Magdeburg (DE). URL: https://patents.google.com/patent/US20230377720A1/en.

# Publication With Authors In Alphabetic Order

## Original works in peer-reviewed international journals

[DP 9] A. Cilardo, M. Gagliardi, and D. Passaretti. "Hardware Support for Thread Synchronisation in an Experimental Manycore System". In: Int. J. Grid Util. Comput. 11.1 (2020), 62–71. ISSN: 1741-847X. DOI: 10.1504/ijguc.2020.103970. URL: https://doi.org/10.1504/ijguc.2020.103970.

## Original works in peer-reviewed international conferences

[DP 10] A. Cilardo, M. Gagliardi, and D. Passaretti. "NoC-Based Thread Synchronization in a Custom Manycore System". In: Advances on P2P, Parallel, Grid, Cloud and Internet Computing. Ed. by F. Xhafa, S. Caballé, and L. Barolli. Cham: Springer International Publishing, 2018, pp. 673–682. ISBN: 978-3-319-69835-9.

# Contents

| I | Int   | troduction                                            |                 | xi |

|---|-------|-------------------------------------------------------|-----------------|----|

| 1 | Intro | roduction                                             |                 | 2  |

|   | 1.1   | Motivation                                            |                 | 2  |

|   |       | 1.1.1 Why interventional and multimodality CT matter  | ?               | 3  |

|   |       | 1.1.2 Why KIDS-CT?                                    |                 | 3  |

|   |       | 1.1.3 Why a CT scanner for multimodality/intervention | al like KIDS-CT |    |

|   |       | is a CPS?                                             |                 | 3  |

|   |       | 1.1.4 Why use MPSoC-FPGAs?                            |                 | 3  |

|   | 1.2   | Research Questions                                    |                 | 4  |

|   | 1.3   | Research Contributions                                |                 | 4  |

|   | 1.4   | Thesis Outline                                        |                 | 5  |

| 2 | Tec   | hnical Background                                     |                 | 7  |

|   | 2.1   | Cyber-Physical Systems                                |                 | 7  |

|   |       | 2.1.1 Physical environment                            |                 | 8  |

|   |       | 2.1.2 Embedded system                                 |                 | 8  |

|   |       | 2.1.3 Physical architecture                           |                 | 9  |

|   | 2.2   | Multi-Processor System-on-Chip Field-Programmable Ga  | te Array        | 10 |

|   |       | 2.2.1 On-chip communication architecture              |                 | 11 |

|   | 2.3   | Mixed-Criticality Systems                             |                 | 13 |

|   |       | 2.3.1 Shared resources in MCSs                        |                 | 14 |

|   |       | 2.3.2 CPSs and MCSs                                   |                 | 14 |

|   |       | 2.3.3 MPSoC-FPGAs for MCSs                            |                 | 14 |

|   | 2.4   | Interventional Computed Tomography                    |                 | 15 |

|   |       | 2.4.1 CT scanner fundamentals                         |                 | 15 |

|   |       | 2.4.2 KIDS-CT scanner                                 |                 | 16 |

|   |       | 2.4.3 CT reconstruction theory                        |                 | 19 |

|   | 2.5   | Design Space Exploration                              |                 | 27 |

|   |       | 2.5.1 Data formats for number representation          |                 | 28 |

| 3 | Rela  | ated Works                                            |                 | 30 |

|   | 3.1   | System Architecture In CPSs                           |                 | 30 |

|   | 3.2   | Control And Data Acquisition Systems                  |                 | 32 |

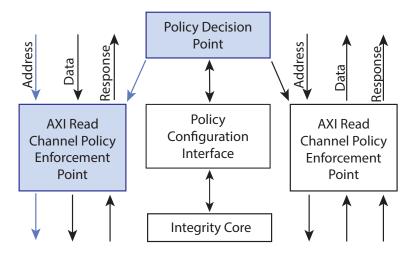

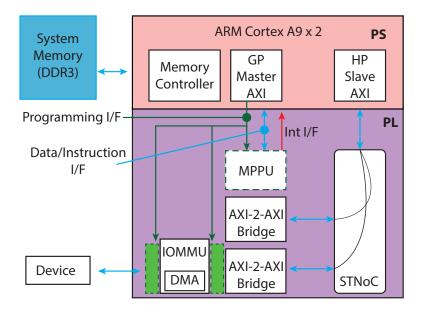

| 3.3 | Task A | And Peripheral Isolation                                   | 36 |

|-----|--------|------------------------------------------------------------|----|

|     | 3.3.1  | Isolation in AMD-Xilinx architectures                      | 36 |

|     | 3.3.2  | Protection units solutions                                 | 38 |

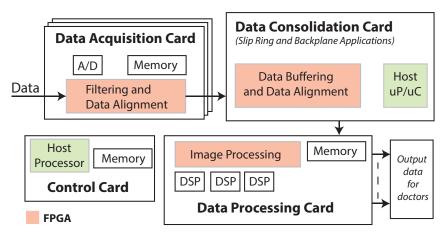

| 3.4 | Comp   | uted Tomography                                            | 41 |

|     | 3.4.1  | Controlling and data acquisition systems for CT scanners   | 41 |

|     | 3.4.2  | The data format exploration in CT data processing $\hdots$ | 43 |

|     |        |                                                            |    |

# II Concept

# 46

| 4 | Prol | blem A  | nalysis                                            | 48 |

|---|------|---------|----------------------------------------------------|----|

|   | 4.1  | Weakr   | ness Of The Current Architectures                  | 48 |

|   | 4.2  | Resear  | rch Questions & Objectives                         | 50 |

| 5 | Met  | hodolo  | gy                                                 | 52 |

|   | 5.1  | Requir  | rement Definition For The Selected CPS Application | 52 |

|   | 5.2  | System  | n Architecture                                     | 53 |

|   | 5.3  | Comm    | nunication Infrastructure                          | 53 |

|   | 5.4  | Contro  | ol-Data Acquisition System                         | 54 |

| 6 | Cyb  | er-Phy  | sical System Architecture                          | 55 |

|   | 6.1  | Requi   | rement & Task Classification                       | 55 |

|   | 6.2  | System  | n Architecture                                     | 56 |

|   | 6.3  | Comm    | nunication Infrastructure                          | 58 |

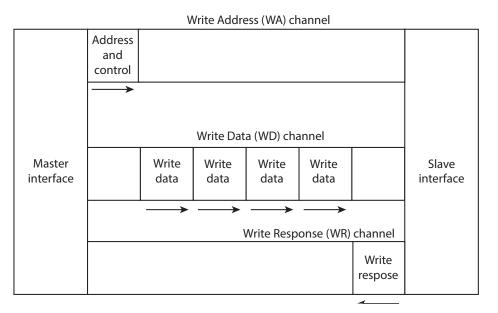

|   |      | 6.3.1   | Communication interface layer                      | 60 |

|   |      | 6.3.2   | Transport protocol layer                           | 61 |

|   |      | 6.3.3   | Application protocol layer                         | 61 |

| 7 | Con  | trol-Da | ata Acquisition System                             | 66 |

|   | 7.1  | Task I  | Partitioning                                       | 66 |

|   | 7.2  | Hardw   | vare/Software Architecture                         | 67 |

|   | 7.3  | Contro  | ol-Synchronization Module                          | 69 |

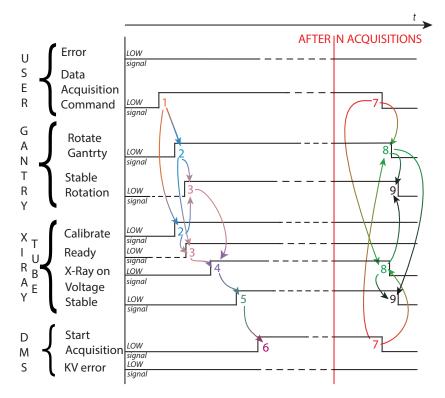

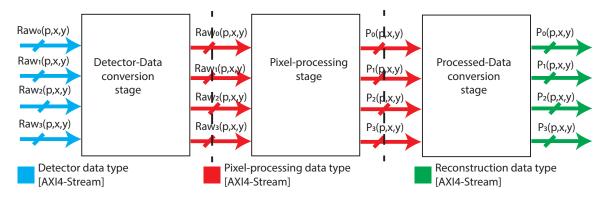

|   |      | 7.3.1   | Hardware layer                                     | 69 |

|   |      | 7.3.2   | Application layer                                  | 73 |

|   |      | 7.3.3   | Example                                            | 75 |

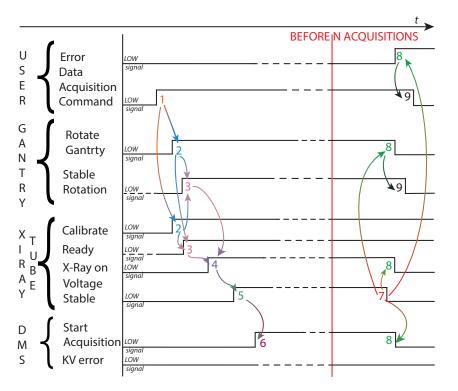

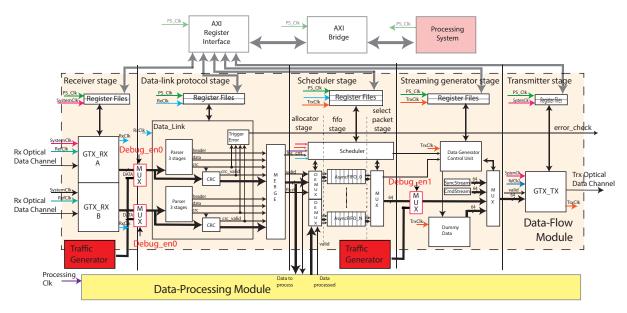

|   | 7.4  | Data-l  | Flow Module                                        | 77 |

|   |      | 7.4.1   | Architecture reconfigurability                     | 78 |

|   |      | 7.4.2   | Inter-clock domains                                | 80 |

|   |      | 7.4.3   | Architecture description                           | 81 |

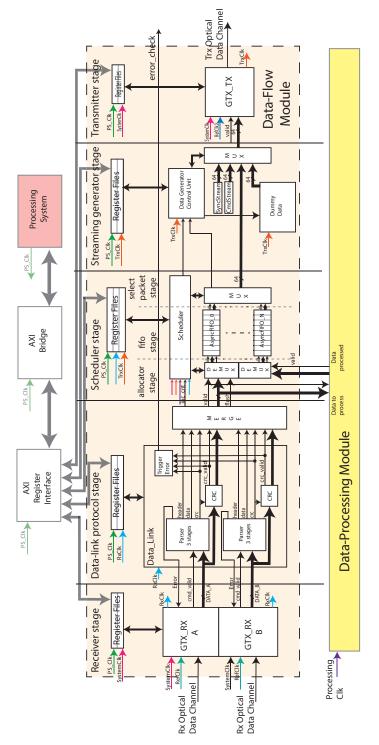

|   | 7.5  | Data-l  | Processing Module                                  | 84 |

|   |      | 7.5.1   | Architecture description                           | 84 |

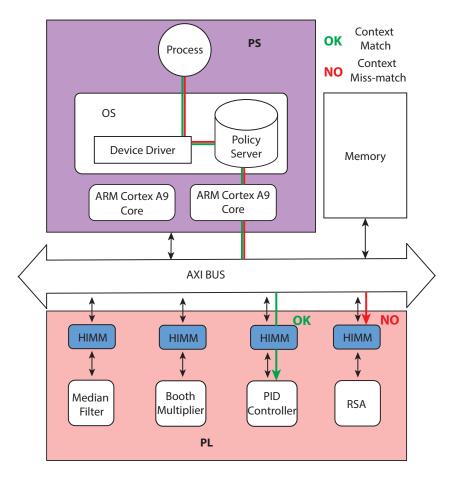

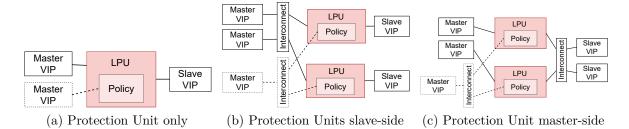

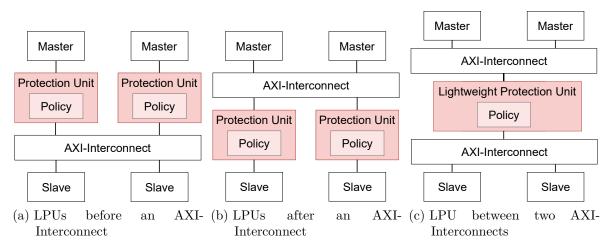

| 7.6 | Isolati | on Support For MPSoC-FPGAs | 86 |

|-----|---------|----------------------------|----|

|     | 7.6.1   | LPU architecture           | 88 |

|     | 7.6.2   | Example                    | 89 |

# III KIDS-CT

# 92

120

| 8 | Syst | tem Architecture For The KIDS-CT Scanner                                                                                                                          | 94 |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 8.1  | CT Requirement Classification                                                                                                                                     | 94 |

|   | 8.2  | System Architecture                                                                                                                                               | 95 |

|   | 8.3  | Communication Infrastructure                                                                                                                                      | 97 |

|   | 8.4  | Optimization Of The Acquisition And Processing Datapath                                                                                                           | 99 |

| 9 | Con  | trol-Data Acquisition System For The KIDS-CT Scanner 1                                                                                                            | 02 |

|   | 9.1  | Hardware/Software Architecture                                                                                                                                    | 02 |

|   | 9.2  | Control-Synchronization Module                                                                                                                                    | 03 |

|   |      | 9.2.1 Software architecture                                                                                                                                       | 04 |

|   |      | 9.2.2 Hardware architecture                                                                                                                                       | 04 |

|   | 9.3  | Data-Flow Module                                                                                                                                                  | 06 |

|   | 9.4  | Data-Processing Module                                                                                                                                            | 09 |

|   | 9.5  | Pixel Processing Optimization                                                                                                                                     | 10 |

|   |      | 9.5.1 I0-correction step                                                                                                                                          | 11 |

|   |      | 9.5.2 Cosine weighting and redundancy weighting steps                                                                                                             | 12 |

|   | 9.6  | Design Space Exploration                                                                                                                                          | 15 |

|   |      | 9.6.1 Selection of input parameters                                                                                                                               | 16 |

|   |      | 9.6.2 Selection of metrics $\ldots \ldots \ldots$ | 17 |

|   | 9.7  | Component Isolation                                                                                                                                               | 18 |

# **IV Validation & Evaluation**

| 10 | Validation                                                                                                                                                         | 122 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 10.1 Validation methodology $\ldots \ldots \ldots$ | 122 |

|    | 10.2 CDAS Design Phase                                                                                                                                             | 123 |

|    | 10.3 CDAS Post-Implementation Phase                                                                                                                                | 125 |

|    | 10.4 KIDS-CT Post-Integration Phase                                                                                                                                | 126 |

| 11 | Performance Evaluation                                                                                                                                             | 127 |

|    | 11.1 CDAS Architecture For The KIDS-CT Scanner                                                                                                                     | 127 |

|    | 11.2 Data-Flow Module                                                                                                                                              | 130 |

|    | 11.2.1 Timing Analysis                                                                                                                                             | 132 |

|    |             | Data-Processing Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 12 |             | gn Space Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 139 |

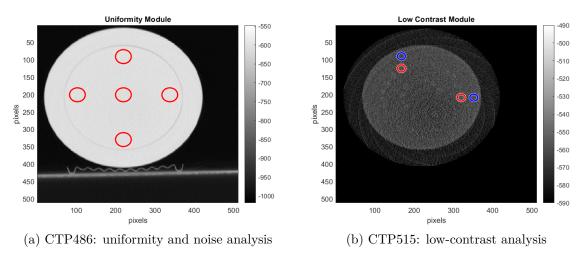

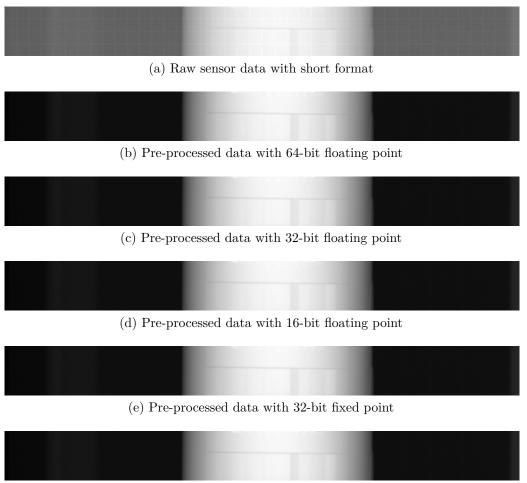

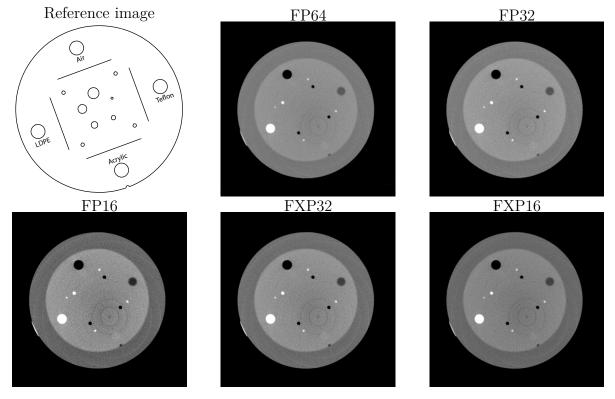

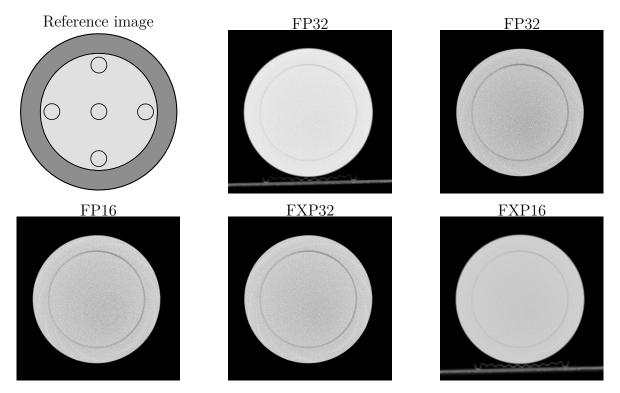

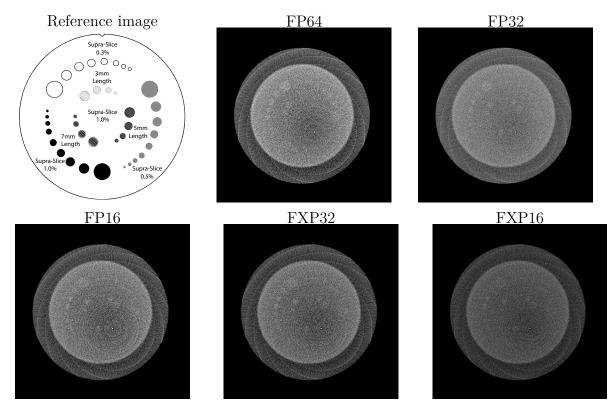

|    | 12.1        | Image Quality Prerequisites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 139 |

|    |             | 12.1.1 CT scanning configuration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140 |

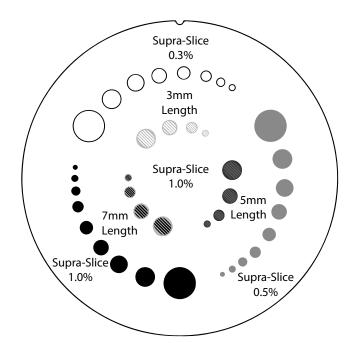

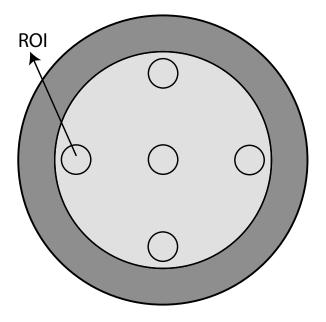

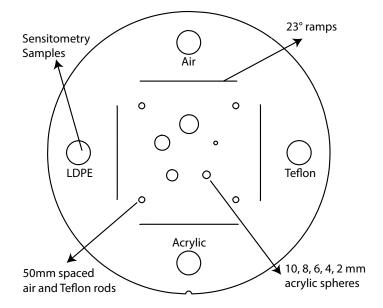

|    |             | 12.1.2 Phantom selection $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 141 |

|    |             | 12.1.3 Calculation of the image quality metrics $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143 |

|    | 12.2        | Image Quality Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 144 |

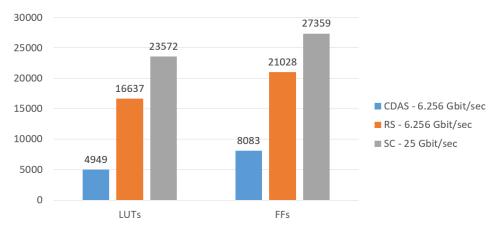

|    | 12.3        | Hardware Cost & Computing Performance $\hdots \hdots \hdo$ | 149 |

|    | 12.4        | Design Space Exploration Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 151 |

| 13 | Eval        | uation Of Functionalities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 152 |

|    | 13.1        | Plug-and-Play Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 152 |

|    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|    | 13.2        | Real-Time Support $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 154 |

|    |             | Real-Time Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| v  | 13.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| •  | 13.3<br>Fir | Comparison With Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 155 |

| 14.2 Discussion Of Results                                           | 162 |

|----------------------------------------------------------------------|-----|

| 14.3 Future Work: Adaptive Computing Acceleration Platforms For CDAS | 164 |

| List of Figures                                                      | 165 |

| List of Tables                                                       | 168 |

| List of Acronyms                                                     | 169 |

| Bibliography                                                         | 176 |

# Part I

Introduction

# **1** Introduction

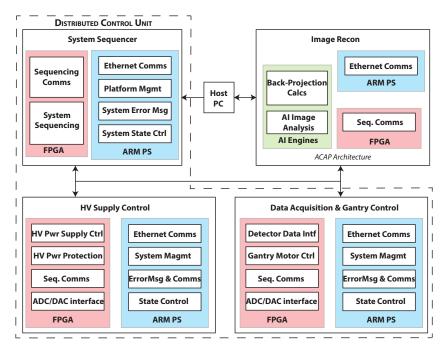

Interventional Computed Tomography (iCT) procedures are increasingly being used to treat the growing number of tumors. To perform such medical procedures, surgeons need Computed Tomography (CT) scanners capable of acquiring and reconstructing images in real time. In such an environment, these devices can be modeled as Cyber-Physical Systems (CPSs), where different sensors/actuators need to be controlled and synchronized while data are acquired and processed in real time [1]. Due to the interoperability difficulties between components from different vendors that often acquire and store data offline, supporting plug-and-play capability and real-time controlling/synchronization and data processing is still an open challenge for many CPS applications, like in CT scanners [2–4]. Often, these tasks are distributed across different Control System (CS) and Data Acquisition System (DAS) architectures [5].

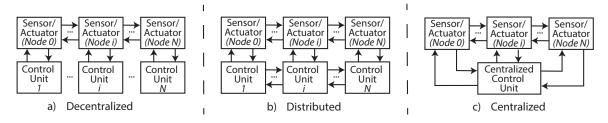

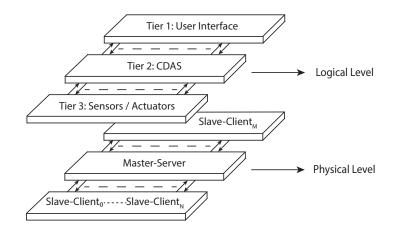

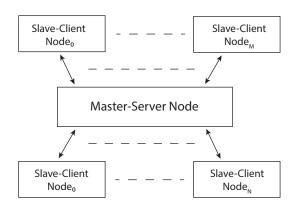

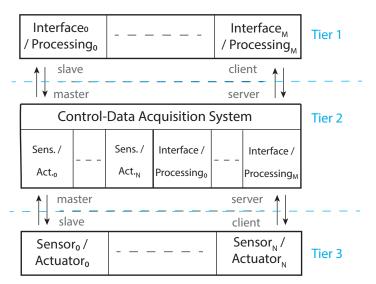

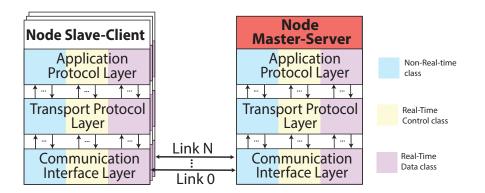

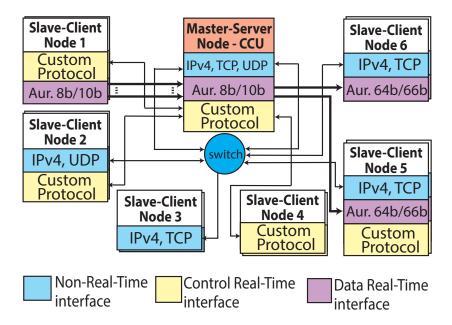

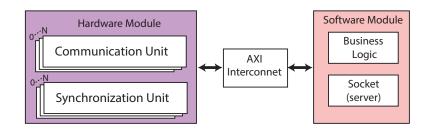

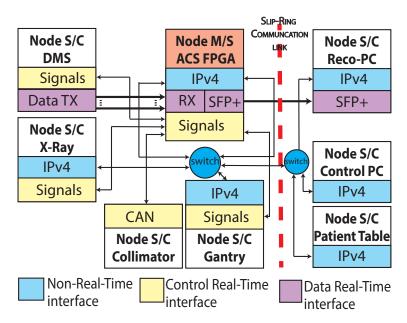

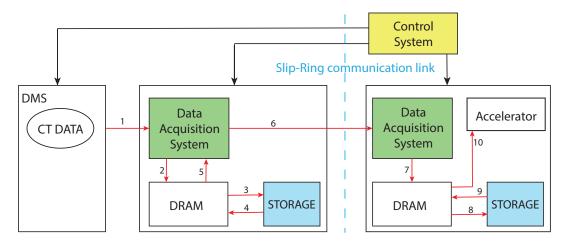

This thesis addresses these challenges and proposes a solution considering the CPS System Architecture, its Communication Infrastructure, and the Control-Data Acquisition System (CDAS) architectures. A Centralized System Architecture not only enhances interoperability for plug-and-play capabilities but also improves the estimation of Worst-Case Execution Time (WCET) for communication tasks which are typically distributed across various components. The Communication Infrastructure employs distinct "layers" and "classes" to segregate control/data and non-real-time/real-time tasks. In contrast to other systems where CS and DAS exist in separate architectures, all these elements permit to join Control and Data Acquisition architectures in a novel CDAS architecture based on MPSoC-FPGA platforms. In this way, the various components are coordinated within a single chip where also data are processed, while the plug-and-play capability and the real-time support are provided in the target CPS. Indeed, this new hardware/software architecture is responsible for controlling/synchronizing CPS device components while data are being acquired and processed on the fly. Finally, in order to demonstrate the impact of the proposed solution, this work focuses on the iCT application and the "Konfigurierbarer, Interfaceoffener, Dosissparender Computertomograph (KIDS-CT)" scanner, where it has been realized, validated and evaluated.

## 1.1 Motivation

The motivation for this thesis is manifold. Starting from the relevance of the targeted application and its impact, the motivation can be condensed to the following questions:

## 1.1.1 Why interventional and multimodality CT matter?

The increasing number of tumors is pushing researchers to explore new medical procedures where single or combined radiological images are used during diagnosis and surgery [6]. Since CT imaging is one of the most effective support in cancer diagnosis, surgeons started to exploit it during tumor ablation [7]. Due to the different application requirements associated to interventional procedures, different radiology scanners can be used. For this purpose, these must be synchronized to generate images simultaneously and obtain useful combined images. So, this CT multimodality imaging became a key element during interventional procedures, contrasting tumors [8]. These factors motivate researchers and underscore the importance of these CT procedures for health and human life. In addition, to fulfill the requirements of this new CT application, the real-time support and the plug-and-play capability became essential requirements for their realization.

## 1.1.2 Why KIDS-CT?

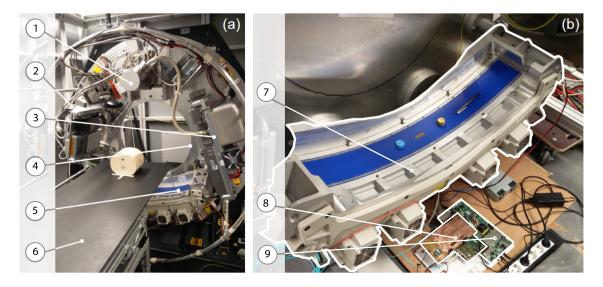

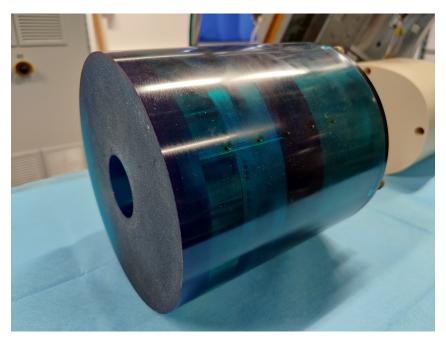

"KIDS-CT" is the first open-interface CT scanner assembled by and in Academia [9]. It is an open-interface CT platform where it is possible to add and exchange components such as X-ray tubes and detector systems in a plug-and-play fashion. Moreover, it has been designed to exploit and explore multimodality techniques. For instance, it can be combined with other devices like Time-of-Flight cameras and Ultrasound scanners. These features allow researchers to explore and test new reconstruction algorithms and new sensors/actuators suitable for new diagnostic and interventional procedures [10].

## 1.1.3 Why a CT scanner for multimodality/interventional like KIDS-CT is a CPS?

A CT scanner for diagnostic procedures acquires and reconstructs images offline without real-time interactions between the physical and the cyber world [11]. In contrast, scanners for iCT procedures provide real-time images used to control the needle insertion and its position inside the patient's body. These real-time images guide surgeons in the tumor ablation intervention [12, 13]. In addition, based on the needle position, the scanner parameters are manually or automatically adjusted to save X-ray doses. This medical procedure is a mere example of real-time interaction between the cyber and the physical world, given by the CT scanner and surgeon/patient, respectively. This real-time interaction defines the distinction between an embedded system and a CPS, such as the KIDS-CT scanner.

## 1.1.4 Why use MPSoC-FPGAs?

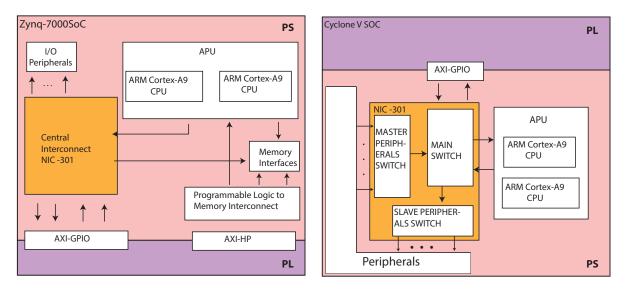

As explained above, a CT scanner for interventional procedures can be modeled as a CPS, where tasks are executed in real time, and the plug-and-play capability should

be provided for enabling multimodality techniques. To fulfill these strict requirements, powerful reprogrammable architectures are the most suitable platforms [14]. In recent years, MPSoC-FPGAs have become the de-facto architecture for reprogrammable architectures [15]. They offer the computation capability of an accelerator and the hard-ware/software reprogrammability capability that gives the flexibility to extend the architecture for new components and use cases, such as in the targeted medical application [10, 16]. Furthermore, these platforms are suitable for ensuring the security and the dependability level of these Mixed-Criticality Systems (MCSs) such as the KIDS-CT scanner, providing different levels of security and isolation between tasks and peripherals associated with different application domains.

# 1.2 Research Questions

Pursued by the importance of providing an open-interface CT scanner such as the KIDS-CT scanner for interventional and multimodality exploration and by the offered potentiality of the MPSoC-FPGA platform in providing real-time support and plug-and-play capability in CPS applications, this work will answer the following research questions:

- How can a CS and a DAS be combined into a CDAS architecture for MPSoC-FPGAs targeting CPS applications such as the KIDS-CT scanner?

- How can CDAS tasks be partitioned on MPSoC-FPGAs to provide real-time support and plug-and-play capability?

- How can a CDAS architecture be designed for an MPSoC-FPGA to acquire and process data on the fly?

- Which data formats optimize computing performance and hardware cost of the CT pre-processing steps while keeping the image quality suitable for iCT?

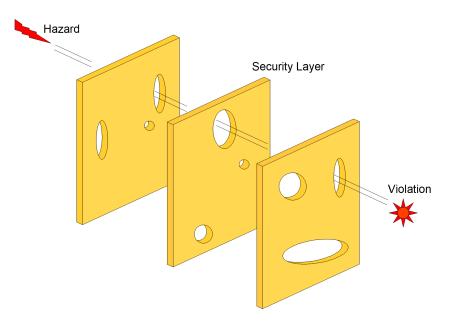

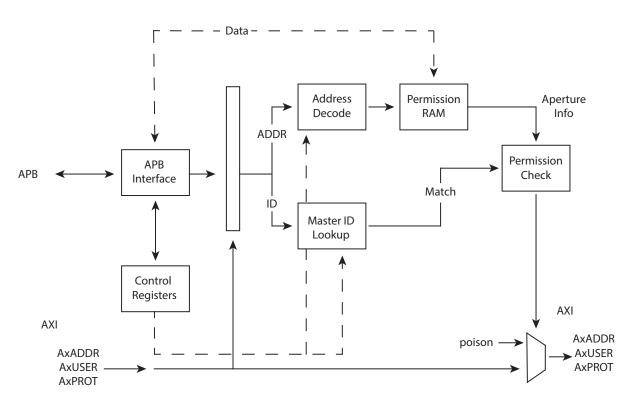

- How can task isolation be achieved in low-cost MPSoC-FPGAs while adhering to the specific requirements of CPSs as MCSs?

# 1.3 Research Contributions

In relation to the above questions, this work provides the following research contributions:

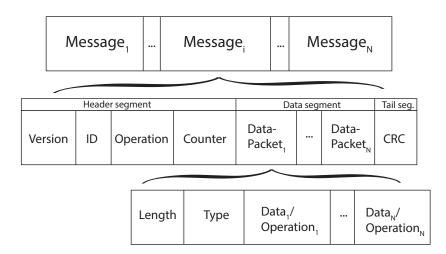

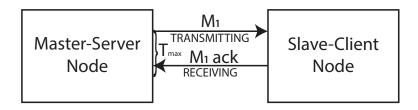

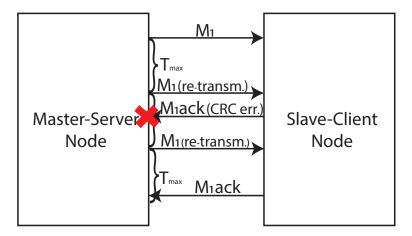

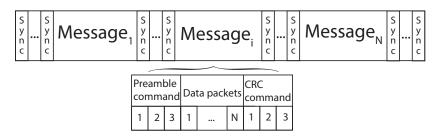

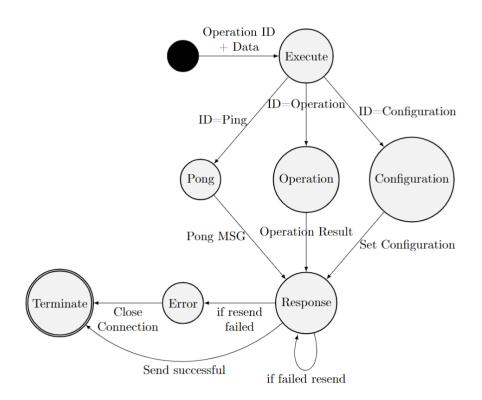

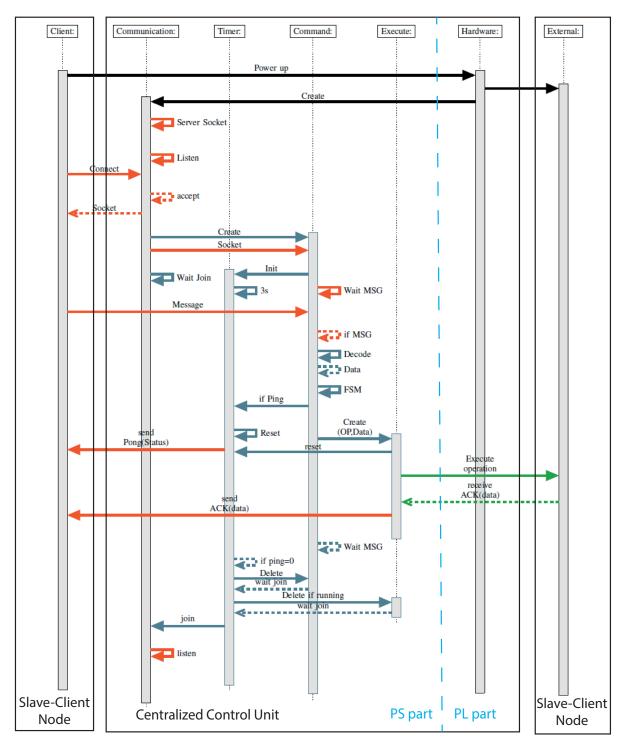

• A Communication Infrastructure with the related centralized control unit that supports custom and standard vendor-protocols. It also proposes various application protocols for real-time and non-real-time commands and data communication tasks. Here, the centralized control unit is part of the proposed CDAS. This solution, facilitates the interoperability between CPS components and the support for plugand-play capability within CPS devices [DP 2].

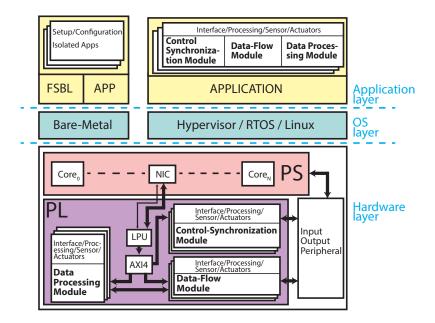

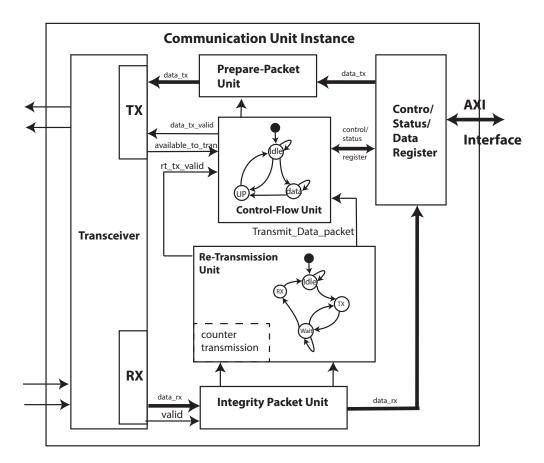

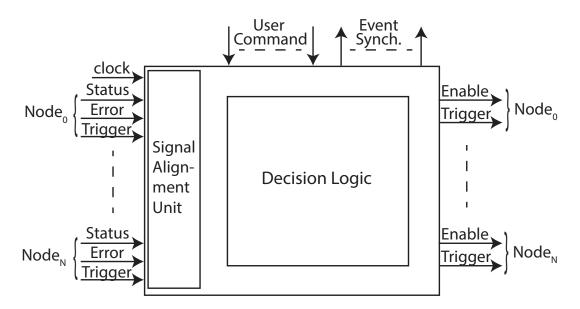

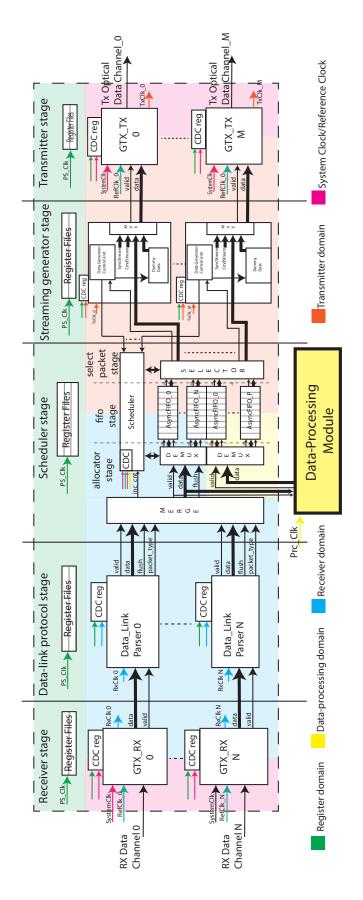

- A hardware/software architecture for CDAS within CPS applications. The proposed architecture targets MPSoC-FPGAs. It provides support for real-time data processing and plug-and-play capability for adding components to the CPS. It is also optimized for iCT applications [DP 3, DP 4].

- A system architecture for diagnostic and interventional CT that guides hardware and system designers in identifying design requirements of a Medical Cyber-Physical System (MCPS) like the different CT scanners [DP 3].

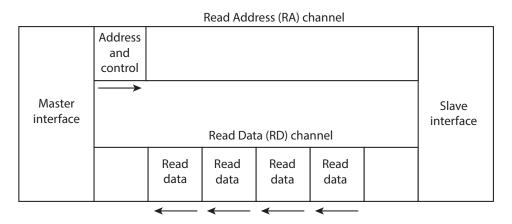

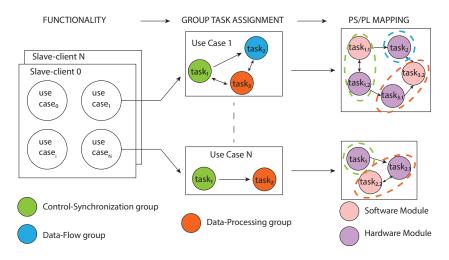

- A task partitioning methodology for MPSoC-FPGAs, where control, communication, and processing tasks are distinguished and mapped on Processing System (PS) and Programmable Logic (PL) in relation the timing requirements and criticality [DP 4].

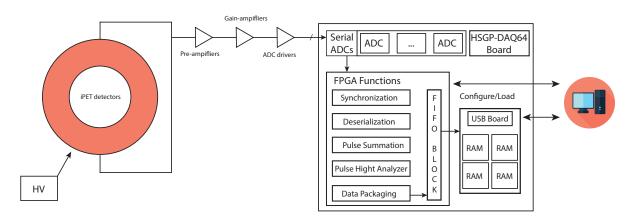

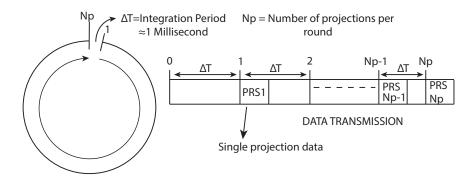

- A lightweight dataflow architecture that can be configured at design time and run time for collecting data from various devices with different acquisition requirements (e.g., various protocols and data rates) [DP 5].

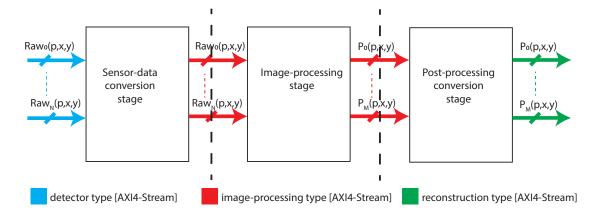

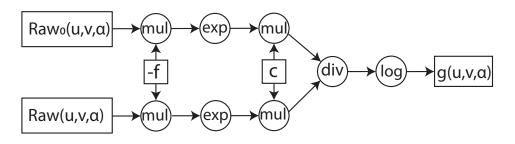

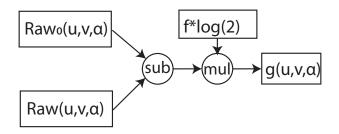

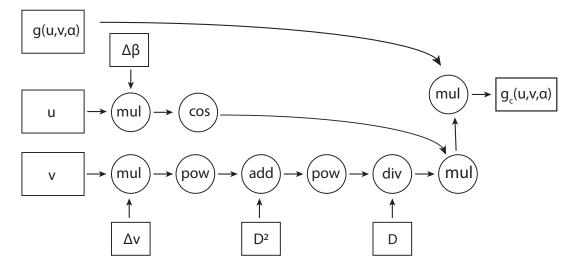

- A processing core architecture for real-time data processing, configurable for standard and custom data formats. In this processing core, a hardware optimization of the algorithm for the I0-correction CT pre-processing step is proposed [DP 1].

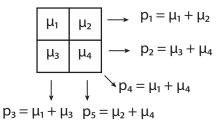

- A Design Space Exploration (DSE) of data formats applied to CT data in the pre-processing steps of the Feldkamp, Davis, and Kress (FDK) algorithm [DP 1].

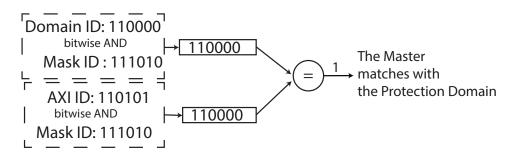

- An isolation method for MPSoC-FPGAs that allows guaranteeing temporal and spatial isolation [DP 6].

- An MPSoC-FPGA prototype of the proposed architecture, integrated into the KIDS-CT scanner. Here, it is responsible for controlling and synchronizing the various internal components and collecting and pre-processing data in real time [9].

# 1.4 Thesis Outline

Part I, containing this Chapter, introduces the research area of this thesis. Chapter 2 explains the technical background on which this work is based on. Subsequently, Chapter 3 provides an overview of the related work, focusing on hardware/software architectures for controlling components and acquiring data in CPSs for medical applications.

Part II explains the process that led the author to the plug-and-play real-time architecture. Here, Chapter 4 systematically defines the problems of actual CPS devices and in the specific case of the iCT application, and Chapter 5 illustrates the proposed methodology for this research work. Then, Chapter 6 and Chapter 7 describe the proposed System Architecture with the Communication Infrastructure, and the CDAS architecture for CPS devices, respectively. This last Chapter describes the different aspects of the CDAS architecture that contribute to achieving the research objectives.

Part III focuses on the targeted CPS use case: the KIDS-CT scanner. Here, Chapter 8 defines the requirements and describes how the proposed methodology and System Architecture for CPSs fits to model the KIDS-CT scanner. Chapter 9 then illustrates the CDAS architecture implemented on the XC7Z045 MPSoC-FPGA and integrated into the KIDS-CT scanner. This includes all the proposed mapping solutions, the modules for controlling-synchronizing components, and for collecting and processing data in real time. Furthermore, this Chapter focuses on the specific optimization proposed for the pixel processing part of the FDK algorithm, which is implemented in the CT reconstruction system. In addition, it describes how metrics and parameters have been selected to explore the design space related to the pixel processing part.

Part IV discusses the validation and evaluation of the proposed work, focusing on its realization and implementation for the KIDS-CT scanner use case. Here, Chapter 10 explains how the CDAS architecture was validated in the design, in the post-implementation, and in the post-integration phases, along with the System Architecture and the Communication Infrastructure. Chapter 11 evaluates the computing performance and the hardware cost of the implemented CDAS architecture implemented for the KIDS-CT scanner; it also considers other configurations of the different modules to show how the proposed architecture can also be extended to support additional components. Chapter 12 reports the results of the image quality analysis applied to the reconstructed images, where different data formats have been used in the reconstruction algorithm; it explores the design space, considering which data format is more suitable for interventional procedures. Chapter 13 evaluates and compares the proposed functionalities with the related work, focussing on the plug-and-play capability and real-time support.

Finally, in Part V, Chapter 14 concludes this thesis by discussing the achieved research objective and presenting open problems for future research work.

# 2 Technical Background

This Chapter introduces the fundamental concepts on which this thesis is based on. Initially, it defines a CPS device, clarifying the difference with an Embedded System (ES). In this context, it reports the various aspects of designing CPSs and introduces the case of MCSs, which are computing systems like KIDS-CT that can run tasks of different criticality. Then, it describes the MPSoC-FPGA, which is the ES platform selected for the proposed CDAS architecture. It also discusses the hardware isolation challenges focusing on the targeted platform. After that, it describes the background of the CT application, focusing on the KIDS-CT scanner that is the selected CPS use case of this thesis. Finally, it explains the fixed-point and floating-point representations used in this work as input parameters of the DSE for the CT pre-processing steps. The contents of this Chapter have also been presented by the author in Ref. [DP 1, DP 2, DP 3, DP 4, DP 5, DP 6, DP 7, DP 8].

## 2.1 Cyber-Physical Systems

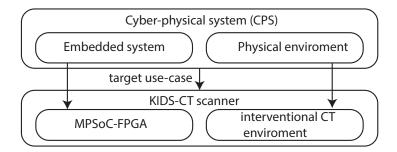

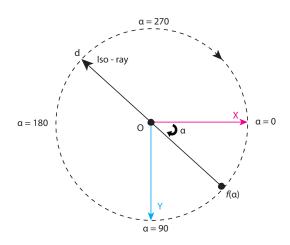

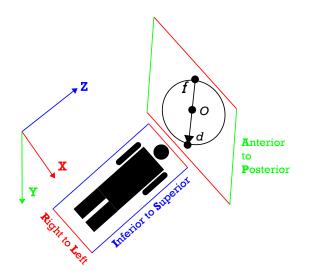

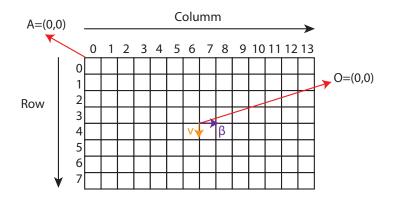

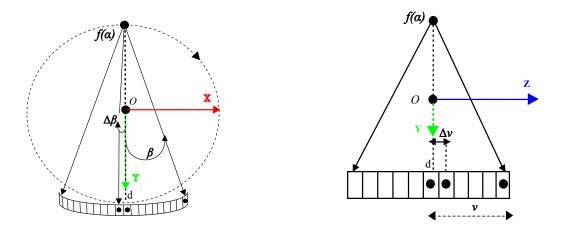

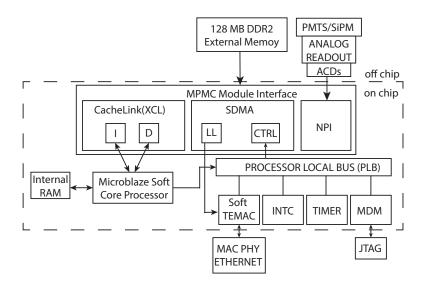

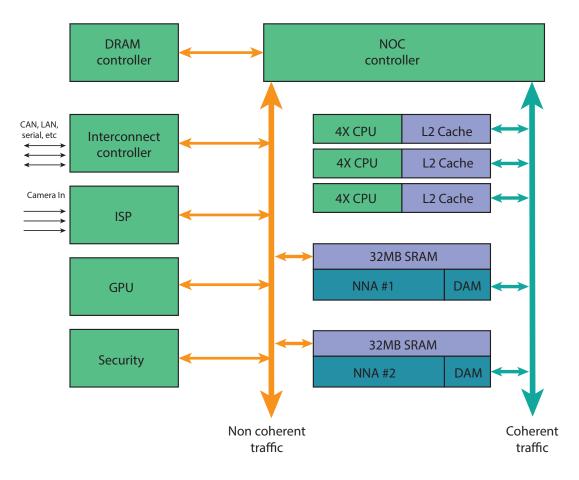

From the computing and communication perspectives, various definitions of Cyber-Physical Systems (CPSs) [17] can be found in the literature. The closest to this work is given by A.E. Lee, who focuses on the computational aspects and defines CPSs as follows: "*Cyber-Physical Systems are integrations of computation and physical processes*" [18]. This definition takes into account two elements: the computation and the physical environment (i.e., physical processes). The link between these two elements allows CPSs to be distinguished from Embedded Systems (ESs), such as smartphones, where there is no physical environment to consider in the modelling and designing process [18]. In fact, "a CPS comprises an embedded system (the information processing part) and a (dynamic) physical environment, or **CPS = ES + (dynamic) physical environment**" [17], as shown in Fig. 2.1.

Figure 2.1: Integration of computation and physical environment

Furthermore, in order to understand the concept of CPS, it is important to define the meaning of "system" E.A. Lee defines it as follows: "A system is simply a combination of parts that is considered as a whole" [18]. In fact, a CPS device can be defined as a system composed of physical subsystems with their interconnections and computing units. For instance, the CT scanner contains several components that are standalone systems; the interaction of these interconnected components with the physical environment constitutes the CT scanner as CPS. Although, there are several definitions of CPSs, which also emphasize the concept of interaction between devices connected to the Internet, this thesis considers CPSs as a device made up of components (sensors/actuators/processing systems) interconnected through a point-to-point connection or a local area network where the hardware platform selected for the ESs becomes crucial. In fact, this research work analyses and proposes solutions to solve problems such as the plug-and-play capability and the real-time support through the use of MPSoC-FPGA platforms, independently of the physical environment of the application.

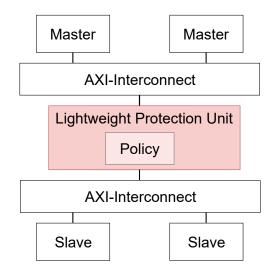

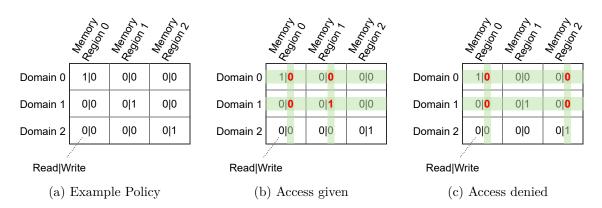

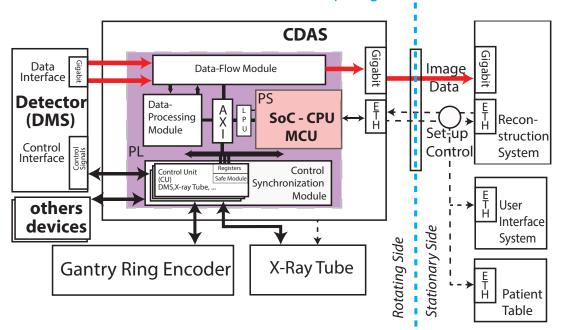

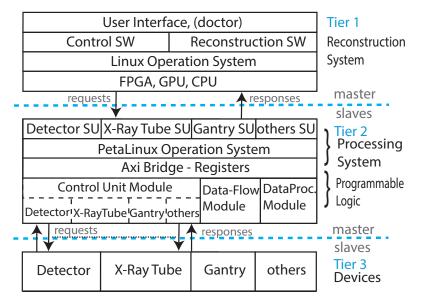

#### 2.1.1 Physical environment