## Konstruktiv hierarchischer Ansatz zur Platzierung und Verdrahtung analoger integrierter Schaltungen

Dissertation

zur Erlangung des akademischen Grades

# Doktoringenieur / Doktoringenieur (Dr.-Ing.)

von Dipl.-Math. Björn Lipka

geb. am 02.07.1978 in Hannover

genehmigt durch die Fakultät für Elektrotechnik und Informationstechnik

der Otto-von-Guericke-Universität Magdeburg

Gutachter: Prof. Dr.-Ing. Wolfgang Mathis

Prof. Dr.-Ing. Heinrich Klar

Prof. Dr.-Ing. Abbas Omar

Promotionskolloquium am 13.02.2012

#### Vorwort

Die vorliegende Arbeit entstand während meiner Zeit als wissenschaftlicher Assistent am Lehrstuhl "Integrierte Schaltungen" der Fakultät Elektrotechnik und Informationstechnik der Otto-von-Guericke Universität Magdeburg.

An dieser Stelle danke ich allen Kollegen an der Universität Magdeburg, die mir in Gesprächen wertvolle Hinweise zur Entwicklung der Programme gegeben haben.

Weiterhin danke ich Herrn Prof. Wolfgang Mathis vom Institut für Theoretische Elektrotechnik der Leibniz Universität Hannover, Herrn Prof. Heinrich Klar vom Institut für Mikroelektronik der Technischen Universität Berlin und Herrn Prof. Abbas Omar vom Institut für Elektronik, Signalverarbeitung und Kommunikationstechnik der Otto-von-Guericke Universität Magdeburg für das Interesse, das sie mit der Übernahme des Referats dieser Arbeit entgegen gebracht haben.

Mein ganz besonderer Dank gilt Herrn Prof. Ulrich Kleine, der mich an der Otto-von-Guericke Universität Magdeburg über die vergangenen Jahre intensiv betreut hat und durch wertvolle Diskussionen und Hinweise einen wesentlichen Anteil am Gelingen dieser Arbeit beigetragen hat.

Natürlich möchte ich auch meiner Familie danken, die mich in all den Jahren meiner Ausbildung unterstützt und somit erst die Grundlage für diese Arbeit geschaffen hat.

#### Kurzfassung

Das Design leistungsfähiger, integrierter Analogschaltungen ist, bedingt durch die große Anzahl variabler Schaltungsparameter, äußerst komplex. Obwohl der Markt im Vergleich zu den digitalen Schaltungen verhältnismäßig klein ist, steigt der Bedarf an analogen Schaltungskomponenten stetig an. Die Layoutsynthese digitaler Schaltungen ist, infolge des Einsatzes automatischer Entwicklungswerkzeuge, mit einem vertretbaren Aufwand zu bewältigen. Demgegenüber werden die Layouts analoger Schaltungen durch die Schaltungsdesigner überwiegend von Hand gezeichnet. Daher ist eine umfassende Unterstützung bei dem Entwurf analoger Schaltungen notwendig. Das Leistungsvermögen und die Einschränkungen eines Werkzeugs haben einen entscheidenden Einfluss auf die Güte und die Kosten der produzierten Schaltungen, sowie auf die notwendigen Ressourcen für den Entwurf. Es ist das automatische Layoutwerkzeug ALADIN entwickelt worden, welches Schaltungsentwicklern die Möglichkeit bietet, spezielles Wissen und Erfahrungen in den Syntheseprozess mit einzubinden, um auf diese Weise qualitativ hochwertige Layouts zu erzeugen.

Im Rahmen dieser Arbeit wird ein sukzessives Platzierungs- und Verdrahtungsverfahren vorgestellt. Aufbauend auf den zu platzierenden Modulen und einer gegebenen Netzlistenbeschreibung wird ein Verbindungsgraph erzeugt. Ein hierarchischer Kompaktierer, der stets zwei Objekte zu einem neuen vereinigt, bildet den Kern des Platzierungsablaufs. Basierend auf dem Verbindungsgraphen wird ein binärer Platzierungsbaum erstellt, der die Reihenfolge und den Zeitpunkt der Kompaktierungen beschreibt. Mit Hilfe eines Entscheidungsbaums werden die geeignete Kompaktierungsrichtung, Orientierung und Topologie der Module jeweils ausgewählt. Nach einem erfolgreichen Kompaktierungsschritt wird automatisch die Verdrahtung der Module durchgeführt und das zugehörige Layout erzeugt. Dazu wird aus der orthogonalen Polygonhülle der Module ein Wegenetz-Graph berechnet. Neben der Auswertung des Graphen unter Verwendung eines Routensuchverfahrens, wird der Einsatz einfacher Leitungselemente zur Realisierung der Verbindung untersucht. Das resultierende Layout des jeweiligen Pfades wird einer Entwurfsregelprüfung mit einer automatischen Korrektur der Regelverletzungen unterzogen.

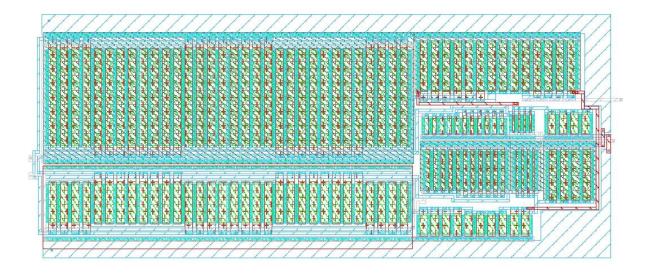

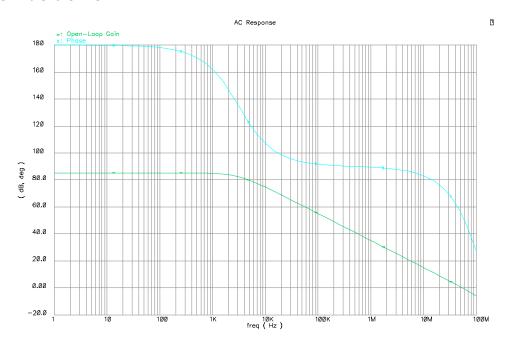

Zur Dokumentation der Leistungsfähigkeit der präsentierten Verfahren sind verschiedene analoge Schaltungen entworfen worden. Für verschiedene Operationsverstärker und Komparatoren werden neben dem Aufbau und den Layouts, die Ergebnisse der Postlayout-Simulationen vorgestellt. Einige der Schaltungen sind in einer 0.25µm CMOS Technologie der Firma IHP GmbH gefertigt worden, u.a. ein neuartiger zweistufiger Kaskoden-Operationsverstärker. Die resultierenden Messergebnisse werden ebenfalls präsentiert.

### Inhaltsverzeichnis

| V  | orwort       |                                                                | 3  |

|----|--------------|----------------------------------------------------------------|----|

| Κι | urzfassung   |                                                                | 5  |

| In | haltsverzeic | hnis                                                           | 5  |

| 1  | Einleitun    | g                                                              | 11 |

| 2  | Passive i    | ntegrierte Elemente                                            | 15 |

|    | 2.1 Einf     | luss des Substrats                                             | 15 |

|    | 2.1.1        | Möglichkeiten zur Reduzierung von Substrateinkopplungen        | 16 |

|    | 2.2 Indu     | ıktivitäten                                                    | 17 |

|    | 2.2.1        | Aufbau integrierter Induktivitäten                             | 17 |

|    | 2.2.2        | Physikalische Effekte                                          | 18 |

|    | 2.2.3        | Modellierung                                                   | 20 |

|    | 2.2.4        | Modulgenerator zur Erstellung von symmetrischen Induktivitäten | 23 |

|    | 2.3 Wid      | erstände                                                       | 25 |

|    | 2.3.1        | Genauigkeit integrierter Widerstände                           | 25 |

|    | 2.3.2        | Einfluss der Temperatur                                        | 27 |

|    | 2.3.3        | Modulgenerator zur Erstellung von Präzisionswiderständen       | 28 |

|    | 2.4 Kap      | azitäten                                                       | 30 |

|    | 2.4.1        | Genauigkeit integrierter Kapazitäten                           | 30 |

|    | 2.4.2        | Modulgenerator zur Erstellung eines binären Kapazitätsfeldes   | 33 |

|    | 2.4.3        | Modulgenerator zur Erstellung von gepaarten Kapazitäten        | 34 |

| 3  | Operatio     | nsverstärker und Komparatoren                                  | 37 |

|    | 3.1 Zwe      | ristufige Operationsverstärker                                 | 37 |

|    | 3.1.1        | Operationsverstärker mit Zero-Nulling Widerstand               | 38 |

|    | 3.1.2        | Operationsverstärker mit Eins-Stromverstärker                  | 40 |

|    | 3.1.3        | Operationsverstärker mit Eins-Verstärker                       | 42 |

|    | 3.2 Zwe      | sistufiger Kaskoden-Operationsverstärker                       | 45 |

|    | 3.2.1        | Design des Kaskoden-Operationsverstärkers                      | 45 |

|    | 3.2.2        | Kleinsignalmodell des Kaskoden-Operationsverstärkers           | 45 |

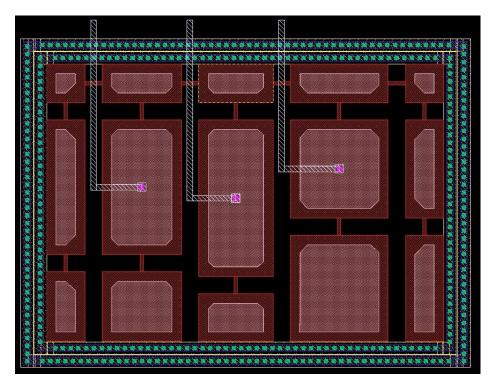

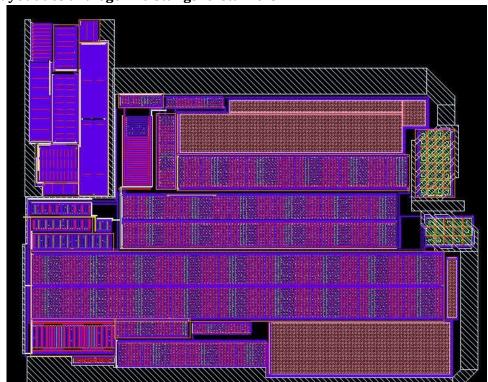

|    | 3.2.3        | Layout des Kaskoden-Operationsverstärkers                      | 48 |

|    | 3.2.4        | Messergebnisse des Kaskoden-Operationsverstärkers              | 49 |

|    | 3.3 Eins     | tufiger Operationsverstärker                                   | 50 |

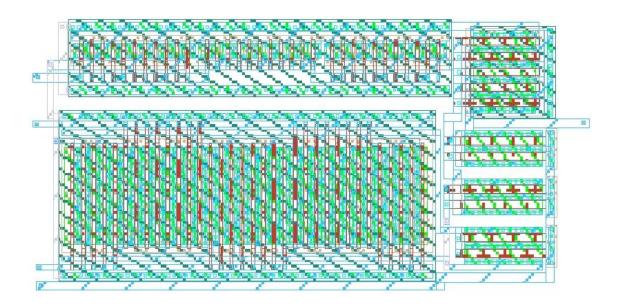

|    | 2 2 1        | Lavout des einstufigen Operationsverstärkers                   | 52 |

8 Inhaltsverzeichnis

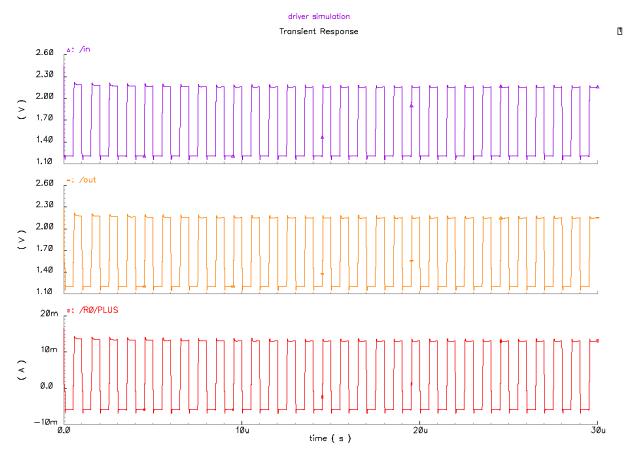

|   |     | 3.3.2 | 2      | Simulationsergebnisse des einstufigen Operationsverstärkers        | . 52 |

|---|-----|-------|--------|--------------------------------------------------------------------|------|

|   | 3.4 | 1     | Ope    | rationsverstärker mit gefalteter Kaskode                           | . 53 |

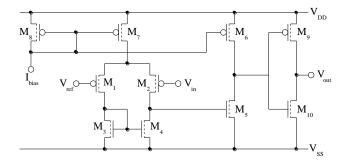

|   |     | 3.4.1 | L      | Design des Operationsverstärkers                                   | . 53 |

|   |     | 3.4.2 | 2      | Kleinsignalmodell des Operationsverstärkers mit gefalteter Kaskode | . 54 |

|   |     | 3.4.3 | 3      | Layout des Operationsverstärkers mit gefalteter Kaskode            | . 55 |

|   |     | 3.4.4 | 1      | Messergebnisse des Operationsverstärkers mit gefalteter Kaskode    | . 56 |

|   | 3.5 | 5     | Anal   | oger Leistungsoperationsverstärker                                 | . 57 |

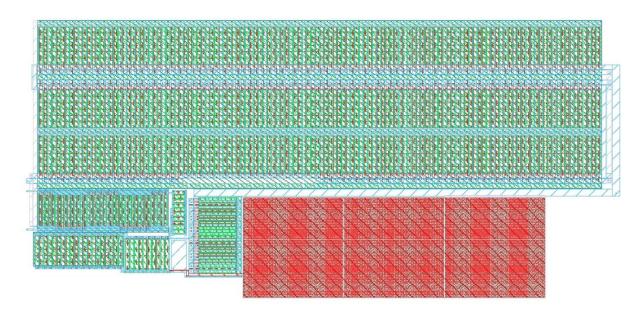

|   |     | 3.5.1 | L      | Layout des analogen Leistungsverstärkers                           | . 59 |

|   |     | 3.5.2 | 2      | Simulationsergebnisse des analogen Leistungsverstärkers            | . 60 |

|   | 3.6 | õ     | Kom    | paratoren                                                          | . 61 |

|   |     | 3.6.1 | L      | Dreistufiger Komparator                                            | . 61 |

|   |     | 3.6.2 | 2      | Dreistufiger SC-Komparator                                         | . 63 |

|   |     | 3.6.3 | 3      | Regenerativer Komparator                                           | . 66 |

| 4 |     | Beka  | annte  | Konzepte zur Platzierung und Verdrahtung                           | . 69 |

|   | 4.1 | l     | Plat   | zierungsverfahren                                                  | . 69 |

|   |     | 4.1.1 | L      | Kräftegesteuerte Platzierung                                       | . 70 |

|   |     | 4.1.2 | 2      | Min-Cut-Platzierung                                                | . 71 |

|   |     | 4.1.3 | 3      | Simulated Annealing                                                | . 73 |

|   |     | 4.1.4 | 1      | Genetische Algorithmen                                             | . 75 |

|   |     | 4.1.5 | 5      | Sonstige Ansätze zur Platzierung integrierter Schaltungen          | . 77 |

|   | 4.2 | 2     | Verd   | drahtungsverfahren                                                 | . 78 |

|   |     | 4.2.1 | L      | Globale Verdrahtung                                                | . 78 |

|   |     | 4.2.2 | 2      | Lokale Verdrahtung                                                 | . 80 |

|   |     | 4.2.3 | 3      | Sonstige Ansätze zur Verdrahtung integrierter Schaltungen          | . 84 |

|   | 4.3 | 3     | Verg   | gleich der vorgestellten Konzepte                                  | . 85 |

| 5 |     | Platz | zierui | ng                                                                 | . 89 |

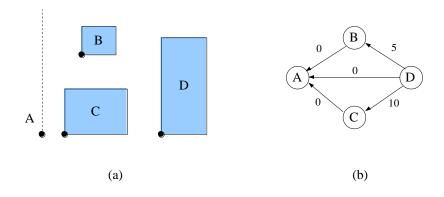

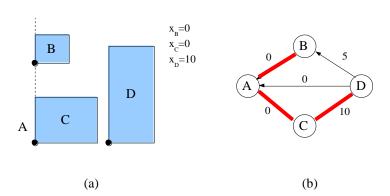

|   | 5.1 | 1     | Idee   | der sukzessiven Platzierung und Verdrahtung                        | . 89 |

|   | 5.2 | 2     | Layo   | outmodell                                                          | . 91 |

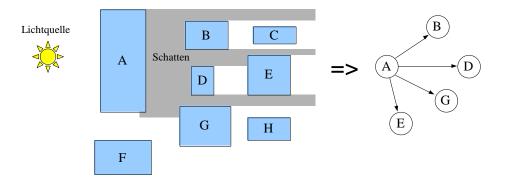

|   | 5.3 | 3     | Verb   | oindungsgraph                                                      | . 94 |

|   | 5.4 | 1     | Kom    | paktierungsverfahren                                               | . 96 |

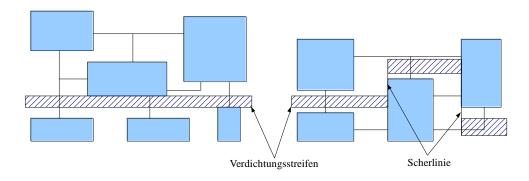

|   |     | 5.4.1 | l      | Modell der Scherlinie                                              | . 97 |

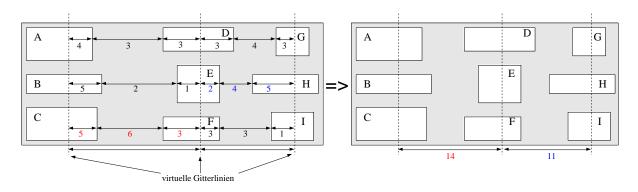

|   |     | 5.4.2 | 2      | Virtuelles Gitter                                                  | . 98 |

|   |     | 5.4.3 | 3      | Restriktionsgraph                                                  | . 99 |

|   |     | 5.4.4 | 1      | Kompaktierung von zwei Zellen                                      | 102  |

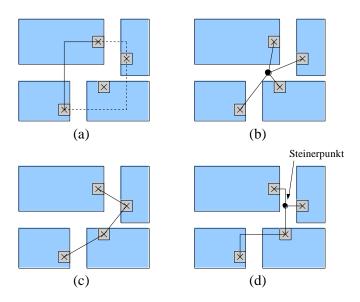

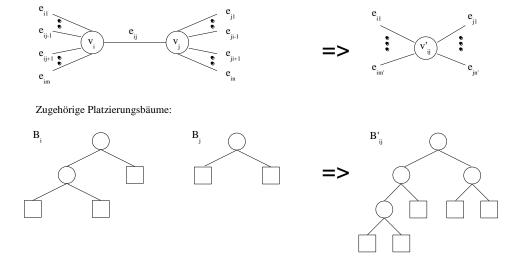

|   | 5.5 | 5     | Aufk   | pau eines binären Platzierungsbaums                                | 104  |

<u>Inhaltsverzeichnis</u> 9

|     | 5.  | 6     | Aus      | wertung des binären Platzierungsbaums                 | 107 |

|-----|-----|-------|----------|-------------------------------------------------------|-----|

|     |     | 5.6.1 | -        | Grundlagen Entscheidungsbaum                          | 108 |

|     |     | 5.6.2 | 2        | Implementierung und Auswertung des Entscheidungsbaums | 109 |

|     |     | 5.6.3 | 3        | Aufbau und Auswertung des Schnittbaums                | 112 |

|     |     | 5.6.4 | ļ        | Entscheidungsregeln                                   | 119 |

|     | 5.  | .7    | Obje     | ektorientierte Implementierung des Platzierers        | 121 |

| 6   |     | Verd  | raht     | ung                                                   | 125 |

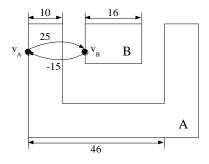

|     | 6.  | 1     | Grui     | ndlegende Vorgehensweise zur Verdrahtung              | 125 |

|     | 6.  | 2     | Aufk     | oau eines Wegenetz-Graphen                            | 127 |

|     | 6.  | .3    | Rou      | tensuche                                              | 131 |

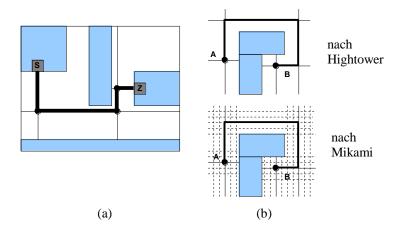

|     |     | 6.3.1 | -        | Darstellung und Analyse von Routensuchverfahren       | 137 |

|     |     | 6.3.2 | 2        | Routensuche mittels Floyd-Warshall Algorithmus        | 139 |

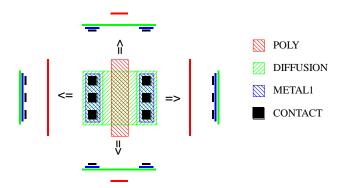

|     | 6.  | 4     | Layo     | outerstellung eines Pfades                            | 144 |

|     |     | 6.4.1 | -        | Erstellen einer Durchkontaktierung                    | 148 |

|     | 6.  | .5    | Prüf     | ung der Entwurfsregeln und der elektrischen Regeln    | 149 |

|     |     | 6.5.1 | -        | Auffinden von Regelverletzungen                       | 150 |

|     |     | 6.5.2 | <u>.</u> | Korrektur von Regelverletzungen                       | 153 |

|     | 6.  | 6     | Obje     | ektorientierte Implementierung des Verdrahters        | 156 |

| 7   |     | Layo  | utbe     | ispiele                                               | 159 |

|     | 7.  | 1     | Zwe      | istufiger Operationsverstärker mit Eins-Verstärker    | 159 |

|     | 7.  | 2     | Ope      | rationsverstärker mit gefalteter Kaskode              | 161 |

|     | 7.  | 3     | Zwe      | istufiger Kaskoden-Operationsverstärker               | 163 |

|     | 7.  | 4     | Einfa    | acher CMOS-Komparator                                 | 166 |

| 8   |     | Zusa  | mme      | enfassung                                             | 169 |

|     | 8.  | 1     | Erge     | bnisse                                                | 169 |

|     | 8.  | 2     | Ausl     | olick                                                 | 170 |

| Α   |     | Erwe  | eiteru   | ungen von ALADIN                                      | 171 |

|     | Α.  | .1    | Tech     | nnoTool                                               | 172 |

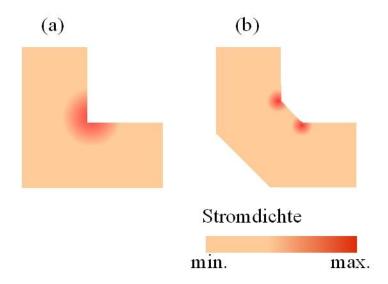

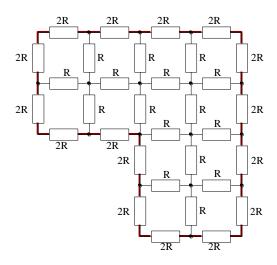

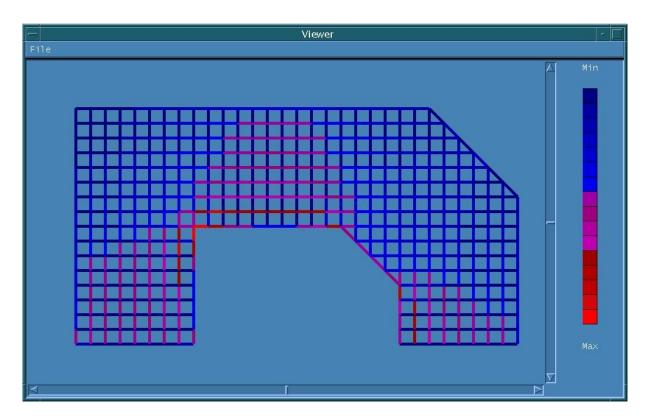

|     | Α.  | .2    | Stro     | mdichtesimulation                                     | 175 |

|     | Α.  | .3    | Wär      | mesimulation                                          | 180 |

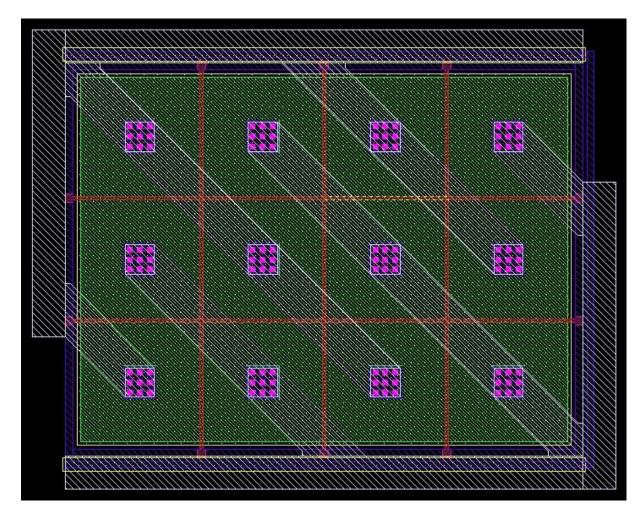

|     | Α.  | .4    | Waf      | fel-Transistor                                        | 183 |

|     |     | A.4.1 | L        | Modulgenerator zur Erstellung von Waffel-Transistoren | 183 |

| В   |     | Besc  | hreil    | oung von Verfahrensabläufen                           | 187 |

| С   |     | Liste | der      | verwendeten Symbole                                   | 189 |

| Lit | ter | atur. |          |                                                       | 193 |

| 10 | Inhaltsverzeichnis |

|----|--------------------|

|    |                    |

| Abbildungsverzeichnis | . 193 |

|-----------------------|-------|

| Tabellenverzeichnis   | . 209 |

| l ehenslauf           | 211   |

#### 1 Einleitung

Bedeutende Fortschritte auf dem Gebiet der Halbleiterfertigungsverfahren haben dazu geführt, dass integrierten Schaltungen in allen Bereichen der technischen Innovation eine zentrale Bedeutung zukommt. Der Bedarf an immer komplexeren Bausteinen mit entsprechend gesteigerter Leistungsfähigkeit und Integrationsdichte ist stetig gestiegen. Um den Entwurf derartig umfangreicher Schaltungen, insbesondere die digitalen Schaltungen, zu bewältigen, sind die Schaltungsdesigner stark abhängig von leistungsfähigen CAD-Werkzeugen. Diese Programme führen die Synthese eines Schaltungsentwurfs von einer Beschreibung bis hin zur Umsetzung in ein Layout durch. Das Leistungsvermögen und die Einschränkungen eines Werkzeugs haben dabei einen entscheidenden Einfluss auf die Güte und die Kosten der zu produzierenden Schaltungen, sowie auf die notwendigen Ressourcen für den Entwurf. Damit ist die Thematik der Entwurfswerkzeuge integrierter Schaltungen ein bedeutender und stetig wachsender Forschungsbereich.

Der Bedarf an anwendungsspezifischen digitalen Schaltungen ist stark angestiegen. Digitale ICs sind sowohl im Schaltbild als auch im Layout verhältnismäßig einfach zu bewältigen. Komplexe Systeme müssen schnell entworfen werden, um dem Wettbewerbsdruck standhalten zu können. Dazu sind in den letzten Jahren eine große Anzahl an Synthese-Werkzeugen auf dem Gebiet der digitalen, integrierten Schaltungen entworfen worden, deren Verbreitungsgrad und Akzeptanz hinreichend groß ist. Der Markt für analoge Schaltungen ist demgegenüber vergleichsweise klein. In diversen komplexeren Schaltungen werden analoge Komponenten vermieden, wenn diese durch eine entsprechende digitale Signalverarbeitung ersetzt werden kann, die zudem durch eine Software implementiert und konfiguriert werden kann. Dennoch ist die Nachfrage nach analogen In Schaltungskomponenten stetig gewachsen. allen Einsatzbereichen Elektronik, Kommunikationstechnik, Steuer- und Regeltechnik, Sensorik oder Konsumelektronik erfordert die Schnittstelle zur Umwelt in den meisten Fällen analoge Signale.

Analoge Schaltungen werden häufig in Handarbeit hergestellt. Sie weisen eine erhebliche Anzahl kritischer Parameter auf, die von der Beschaffenheit des Layouts besonders betroffen sind. Im Gegensatz zu digitalen Schaltungen, wo bei einer Vielzahl an Bauelementen von einer fixen Abmessung ausgegangen werden kann, sind analoge Komponenten einem sehr starken Größenunterschied unterworfen. Dadurch wird der Entwurf der Schaltung und des Layouts erschwert. Obwohl die analogen Komponenten zumeist nur einen kleinen Teil der Chipfläche bei Mixed-Signal Schaltungen benötigen, entfällt der größere Anteil an Zeit- und Entwurfskosten auf diese Schaltungen. Sie sind häufiger verantwortlich für Designfehler und teure Redesigns. Die Ursache liegt im größeren Freiheitsgrad analoger Schaltungen im Vergleich zu den digitalen Schaltungen. Infolge einiger besonderer und notwendiger Nebenbedingungen, wie die große Variation der Transistordimensionen, Empfindlichkeit gegenüber parasitären Kapazitäten oder Symmetriebedingungen, ist der Entwurf analoger integrierter Schaltungen deutlich anfordernder. Auf der einen Seite ist die Anzahl der verschiedenen Elementgruppen, wie Stromspiegel oder Differenzstufen, vergleichsweise gering, andererseits variieren diese Zellen erheblich im Hinblick auf ihre Dimensionen und Lage der Anschlüsse. Die geometrischen Parameter von MOS-Transistoren (Weite, Länge und Faltungsfaktor) können, je nach Anwendung, in einem großen Bereich verändert werden.

12 Einleitung

Im Zuge der Verkleinerung der minimalen Strukturgrüßen auf einem Chip, sowie die wachsenden Anforderungen hinsichtlich eines geringen Leistungsverbrauchs und einer hohen Geschwindigkeit, verschlechtern sich die elektrischen Parameter eines MOS Transistors in Bezug auf analoge Schaltungen zunehmend. Damit nimmt das Designfenster, innerhalb dessen die Dimensionierungen der Elemente gewählte werden können, stetig ab. Eine Optimierung wird im Allgemeinen ohne das Layout durchgeführt. Für die parasitären Elemente wird lediglich eine grobe Abschätzung verwendet. Ebenso wird eine Anwendung verschiedener Topologien nur selten geprüft. Eine verlässliche Optimierung erfordert jedoch Kenntnisse über die elektrischen Parameter, die aus dem Layout hervorgehen, wie beispielsweise parasitäre Kapazitäten, RC-Zeitkonstanten der Gates, Stromdichte oder auch das Temperaturverhalten und die resultierenden Einflüsse.

Aus diesen Gründen ist eine umfassendere Unterstützung beim Design analoger Schaltungen notwendig. Es sind eine Reihe von Forschungsarbeiten auf dem Gebiet der Werkzeuge für den Schaltungsentwurf und die Layouterstellung analoger Schaltungen durchgeführt worden [Cohn94, Rijm89]. Aus den Arbeiten gingen diverse Realisierungen hervor, die bei den Schaltungsdesignern jedoch nur wenig Billigung erfahren haben. Eine Ursache ist darin zu finden, dass es sehr schwierig ist, schnelle und flexible Werkzeuge für jede Stufe der Layoutsynthese zu entwerfen, die stets hochqualitative Layouts hervorbringen. Ein weiterer Grund ist der, dass die Schaltungsdesigner häufig eine geeignete Kontrolle über den Syntheseprozess vermissen. Die Werkzeuge umgehen mehr oder weniger den Designer [Rjim89].

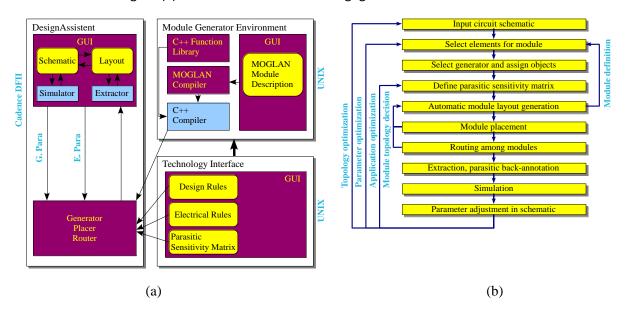

Für gewöhnlich geht die Konstruktion von analogen Layouts eher auf jeden einzelnen Transistor als auf Elementgruppen oder Teilschaltungen ein [Cohn94, Garr88, Garr91, Lamp95, Lamp96a, Lamp96b], wodurch die Komplexität, insbesondere für umfangreiche Schaltungen, ansteigt. Die Flexibilität durch Einbeziehung des Schaltungsdesigners ist teilweise ebenfalls eingeschränkt. Das ALADIN Designpaket (Automatic Layout Design Aid for Analog Integrated Circuits) ermöglicht es Schaltungsdesigner, ihr Wissen in den Syntheseprozess mit einzubringen [Wolf96, Wolf98a, Wolf98b, Wolf99a, Wolf99b, Wolf01, Zhan00, Zhan01, Zhan06a, Zhan06b].

Bedingt durch die Anforderungen analoger Schaltungen, ist es vorteilhafter, einzelne Transistoren zu Blöcken, den sogenannten Makrozellen bzw. Modulen, zusammenzufassen. Damit jeweils ein akzeptables Layout für eine große Anzahl an parametrisierbaren Modulen verfügbar ist, sind entsprechende Modulgeneratoren bereitzustellen. Um die Modulgeneratorbibliothek überschaubar zu halten, aber dennoch optimale Layouttopologien für einen weiten Parameterbereich bereithalten zu können, ist in ALADIN eine Modulgeneratorumgebung implementiert worden. Darin können mit Hilfe einer einfachen, natürlichen Beschreibungssprache technologie- und anwendungsunabhängige Generatoren entwickelt werden. Das konstruktive Modulgeneratorkonzept basiert auf einer relativen Platzierung von Objekten ohne Berücksichtigung der Entwurfsregeln in der Modulbeschreibung. Infolge der automatischen Berücksichtigung dieser Regeln durch die Umgebung, ist das resultierende Layout stets entwurfsregelkonform.

Nach der Erstellung der Topologien bleiben die Modul-Layouts derart anzuordnen, dass der Flächenbedarf und die Leitungslängen, unter Einhaltung weiterer Nebenbedingungen, minimal werden. Es ist jedoch zu beachten, dass sich bei der Verwendung nicht optimaler Module selbst mit aufwändigen Platzierungs- und Verdrahtungsverfahren nur suboptimale Ergebnisse erzielen lassen.

Einleitung 13

Für die vorliegende und die vorhergehenden Arbeiten stand das Designframework II von Cadence zur Verfügung. Aus diesem Grund ist eine Schnittstelle zu dieser Entwicklungsumgebung entworfen worden.

Um die Verlässlichkeit zu gewährleisten, erfolgen die Platzierung und Verdrahtung nahezu simultan. Die Zellen werden sukzessive miteinander in Verbindung gesetzt und positioniert. Damit ist eine gewisse Vorhersagbarkeit gegeben.

Nach diesem einleitenden Kapitel folgt im nächsten Kapitel eine Beschreibung passiver integrierter Elemente. Es wird der Einfluss des Substrats auf die Bauelemente kurz dargestellt und die Möglichkeiten zur Minderung der Substrateinkopplungen beschrieben. Unter Verwendung der MOGLAN Bibliothek werden Modulgeneratoren entworfen, mit denen das Layout von symmetrischen spirale Induktivitäten, Präzisionswiderständen, binären Kapazitätsfeldern und gepaarte Kapazitäten erstellt werden kann. Um die Induktivitäten im Layout simulieren zu können, wird für diese eine entsprechende Modellierung präsentiert. In Kapitel 3 erfolgt eine Beschreibung der im Rahmen dieser Arbeit entstandenen Operationsverstärker und Komparatoren. Für das Layout sind die Zellen mit Hilfe der Modulgeneratorumgebung erstellt worden. Für einen Teil der Operationsverstärker sind Prototypen in einer 0,25µm CMOS Technologie produziert worden, so dass neben den Simulationsergebnissen die entsprechenden Messergebnisse präsentiert werden. Die nähere Erläuterung bekannter Lösungsansätze und -verfahren zur Platzierung und Verdrahtung integrierter analoger Schaltungen sind Bestandteile von Kapitel 4.

In Kapitel 5 wird das in dieser Arbeit entwickelte Verfahren zur Platzierung analoger, integrierter Schaltungen vorgestellt. Zunächst erfolgt eine Beschreibung des Layoutmodells, welches für die Platzierung genutzt wird. Anschließend werden die Schritte erläutert, die notwendig sind, um einen Verbindungsgraphen aus der zu bearbeitenden Schaltung zu erhalten. Aufgrund der Tatsache, dass die Kompaktierung von Modulen ein zentraler Bestandteil der Platzierung in dieser Arbeit ist, wird ein kurzer Überblick zu den verschiedenen Kompaktierungsverfahren gegeben. Basierend auf dem Verbindungsgraphen wird ein binärer Platzierungsbaum erstellt. Dieser Platzierungsbaum legt die Reihenfolge fest, wann die jeweiligen Module kompaktiert und verdrahtet werden sollen. Die Auswertung des Baumes erfolgt in einem Post-Order-Durchlauf. Dabei werden, unter Benutzung von Entscheidungs- und Schnittbäumen, die Lage und Orientierung der Module zueinander ermittelt und anschließend die Platzierung und Verdrahtung der Module durchgeführt.

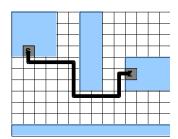

Die Vorgehensweise zur Verdrahtung analoger integrierter Schaltungen wird in Kapitel 6 dargelegt. Basierend auf der orthogonalen Polygonhülle der beteiligten Zellgeometrien wird ein Wegenetz-Graph, der die möglichen Pfade repräsentiert, erstellt. Neben der Anwendung eines Routensuchverfahrens in dem resultierenden Graphen, um zwei Terminals miteinander zu verbinden, wird der Einsatz einfacher Leitungselemente zur Realisierung der Verdrahtung geprüft. Nach der Layouterstellung der ermittelten Routen wird eine Entwurfsregelprüfung mit einer automatischen Korrektur der möglichen Regelverletzungen durchgeführt. Die Leistungsfähigkeit der entworfenen Werkzeuge wird anhand von ausgewählten Beispielen in Kapitel 7 dokumentiert. Abschließend wird in Kapitel 8 eine Zusammenfassung dieser Arbeit ausgeführt. Dabei werden die wichtigsten Ergebnisse in kompakter Form wiedergegeben. Zusätzlich erfolgt ein Ausblick auf zukünftige Arbeiten.

#### 2 Passive integrierte Elemente

Typische integrierte Schaltungen bestehen aus komplexen, miteinander verbundenen und interagierenden Blöcken, die sich aus digitalen, abgetasteten analogen (z.B. SC-Schaltungen bzw. D/A- oder A/D-Umsetzern) und zeitkontinuierlichen analogen Schaltungen zusammensetzen können. Um die beim Design der Schaltung anvisierte Leistungsfähigkeit auch beim gefertigten Schaltkreis zu erzielen, ist es notwendig, parasitäre Effekte und herstellungsbedingte Einflüsse während der Entwurfsphase mit zu berücksichtigen. Neben Transistoren und Dioden werden für analoge Schaltungskomponenten häufig zusätzliche passive Bauelemente benötigt. So finden Induktivitäten in der Hochfrequenztechnik häufig Anwendung in Filtern oder Bias-Netzwerken von Verstärkern, z.B. zur DC-Entkopplung. Integrierte Kapazitäten kommen in SC-Schaltungen, Verstärkern oder Hochfrequenz-ICs zum Einsatz und integrierte Widerstände werden beispielsweise in D/A- bzw. A/D-Umsetzern eingesetzt. Es gibt eine Vielzahl an Einsatzmöglichkeiten und auch eine große Anzahl Realisierungsvarianten für die passiven Bauelemente. Die entscheidenden Kriterien für die Auswahl von verschiedenen Realisierungsmöglichkeiten sind der Nominalwert des Bauelements, die Genauigkeitsanforderungen und parasitäre Effekte, die das entsprechende Bauteil aufweisen kann. Eine hinreichend genaue Einstellung der Verhältnisse der Nominalwerte ist bei den integrierten Schaltungen in der Regel möglich. Hingegen sind größere Toleranzen bezüglich der Absolutgenauigkeit nicht zu vermeiden.

In diesem Kapitel werden zu Beginn der Einfluss des Substrats auf die Bauelemente näher erläutert und Möglichkeiten zur Reduktion von Substrateinkopplungen aufgezeigt. Anschließend wird der Aufbau integrierter Induktivitäten und die wichtigsten auftretenden physikalischen Effekte beschrieben. Es werden eine Modellierung der Induktivität und ein Modulgenerator zur Erstellung symmetrischer spiralförmiger Induktivitäten präsentiert. Im nachfolgenden Abschnitt soll die Genauigkeit von integrierten Widerständen und die Einflussnahme durch die Temperatur diskutiert werden. Außerdem werden Modulgeneratoren zur automatischen Erstellung des Layouts von integrierten Präzisionswiderständen beschrieben. Abschließend erfolgt eine Untersuchung der Genauigkeit von integrierten Kapazitäten und der Präsentation von Generatoren zur Layoutkonstruktion von binären Kapazitätsfeldern und gepaarten Kapazitäten.

#### 2.1 Einfluss des Substrats

Im Gegensatz zu diskret aufgebauten Schaltungen können bei integrierten Schaltungen einzelne Bauelemente nicht für sich allein betrachtet oder modelliert werden. Alle Elemente befinden sich gemeinsam auf demselben Substrat. Dieses Substrat ist kein idealer Isolator, so dass Kopplungen zwischen den Elementen und Schaltungsteilen auftreten. Unter bestimmten Voraussetzungen können einige dieser Kopplungen beim Design vernachlässigt werden, da ihr Einfluss auf die Schaltung gering ist. So fällt nur der Einfluss des Substrats bis zur Kontaktierung ins Gewicht, wenn beispielsweise das Substrat um ein Element oder Schaltungsteil sehr niederohmig mit Masse verbunden wird. In Abhängigkeit von der Empfindlichkeit der Schaltung wird die Verkopplung mit anderen Elementen daraufhin derart klein, dass sie nicht mehr berücksichtigt werden muss.

Um die Art der Verkopplungen genauer beschreiben zu können, soll zunächst auf die Eigenschaften des Substrats näher eingegangen werden.

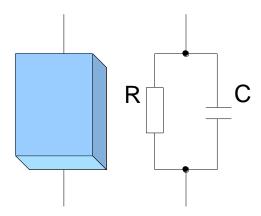

Abbildung 2-1: Ersatzschaltbild eines Substratquaders

Betrachtet man einen Quader innerhalb des Substrats (siehe Abbildung 2-1) und nimmt einen Stromfluss vom oberen zum unteren Rand an, so lässt sich die Impedanz durch das in Abbildung 2-1 dargestellte Ersatzschaltbild beschreiben. Ein genaues Modell besteht also aus einer Vielzahl infinitesimal kleinen Parallelschaltungen von ohmschen Widerständen und Kapazitäten entlang der Richtung des Stroms, für den die Kopplung beschrieben werden soll. Für die Werte von R und C gilt dabei:

$$R = \rho \frac{l}{A'} \tag{2-1}$$

$$C = \varepsilon_0 \varepsilon_r \frac{A}{I},\tag{2-2}$$

$$RC = \rho \varepsilon_0 \varepsilon_r. \tag{2-3}$$

Dabei ist  $\rho$  der spezifische Widerstand, I die Länge des Quaders und A dessen Fläche quer zur Stromrichtung. Die Konstanten  $\epsilon_0$  und  $\epsilon_r$  beschreiben die Dielektrizität des Materials.

Eine einfache Beschreibung ist die Verkopplung durch lediglich eine einzige parallele RC- Schaltung zwischen zwei Punkten in der Schaltung. In den überwiegenden Fällen erweist sich diese Vorgehensweise als hinreichend. Für niedrige Frequenzen kann eine Modellierung der Verkopplung durch das Substrat auch einfach nur durch einen ohmschen Widerstand erfolgen. So ist diese Betrachtung bei der Modellierung des Einflusses von Wirbelströmen, die durch integrierte Induktivitäten hervorgerufen werden, durchaus ausreichend [Pete03].

Alle Kopplungen über das Substrat sind abhängig von der Art der Kontaktierung. Eine Abschätzung der Stärke der Kopplung kann daher erst nach der Fertigstellung des Layouts erfolgen. Aus diesem Grund wird sie in keinem der Modelle für einzelne Bauelemente berücksichtigt [Hein04]. Es ist die Aufgabe des Designers diese Einflüsse so gering wie möglich zu halten, abzuschätzen und in die Nachsimulation nach der Layouterstellung mit einfließen zu lassen.

#### 2.1.1 Möglichkeiten zur Reduzierung von Substrateinkopplungen

Substrateinkopplungen sind insbesondere bei Mixed-Signal Schaltungen zu beobachten, da sich hier die rauschempfindlichen analogen Schaltungskomponenten und die digitalen Schaltungen, die das Rauschen verursachen, auf demselben Substrat befinden. Mit Hilfe eines sorgfältigen Layouts ist jedoch möglich, den Effekt der Substrateinkopplung zu minimieren. Im Folgenden werden die Möglichkeiten der räumlichen Trennung von rauschempfindlichen und rauschenden Komponenten und der Einsatz von Guardringen zur Reduzierung der Substrateinkopplungen näher erläutert.

#### 2.1.1.1 Räumliche Trennung

Ein Lösungsansatz zur Reduzierung der Substrateinkopplungen ist gegeben durch eine räumliche Trennung der rauschempfindlichen Schaltungsbereiche von den stark rauschenden Komponenten. Die Effektivität dieser Vorgehensweise ist jedoch stark abhängig von der Beschaffenheit des Substrats, das zur Herstellung der Schaltung verwendet wird. So wird bei der Fabrikation von integrierten Schaltungen zwischen hochohmigen und niederohmigen Substrat unterschieden [Su93]. Das niederohmige Substrat besteht aus einer schwach dotierten Epitaxie-Schicht oberhalb von der stark dotierten Hauptschicht. Der überwiegende Teil der lateralen Ströme fließt in diesem Fall durch die stark dotierte Schicht, welche sich unter elektrischen Gesichtspunkten damit wie einziger Knoten verhält. Eine räumliche Trennung zwischen Rauschquellen und rauschempfindlichen Strukturen führt in diesem Fall zu keiner signifikanten Reduzierung der Einkopplung [Su93]. Im Gegensatz dazu setzt sich das hochohmige Substrat lediglich aus einer gleichmäßig schwach dotierten Schicht zusammen. Infolge eines fehlenden niederohmigen Bereichs, ist der Stromfluss innerhalb des Substrats weitestgehend gleichmäßig. Aus diesem Grund kann bei Verwendung des hochohmigen Substrats die Isolierung zwischen digitalen und analogen Schaltungsbereichen durch eine Vergrößerung der räumlichen Distanz verbessert werden [Su93].

#### 2.1.1.2 Guardringe

Ein Guardring bezeichnet einen Substraktkontakt, der ringförmig um eine zu schützende Struktur gelegt wird. Ein derartiger Ring wird aus p+-Diffusion bzw. n+-Diffusion gebildet und auf VSS- bzw. VDD-Potential gelegt. Das Ziel eines Guardrings besteht darin, die Ausbreitung von Störungen aus dem Substrat in die Epitaxie-Schicht zu verhindern [Puwa95]. Der Guardring ist dabei so nah wie möglich an die zu schützenden Elemente zu platzieren.

#### 2.2 Induktivitäten

Induktivitäten sind Schlüsselelemente hochfrequenter Schaltungen. Sie werden benötigt, um verlustfreie Anpassungen zu realisieren oder kommen als Lasten bei Schaltungen zum Einsatz, die bei geringen Versorgungsspannungen arbeiten oder schmalbandig sein müssen.

Problematisch ist jedoch die umfassende Modellierung. Insbesondere das Substrat, auf dem sie aufgebracht sind, kann in CMOS nicht als idealer Isolator angenommen werden. Die Folge sind sowohl Verluste durch kapazitive Kopplungen, als auch die Erzeugung von Wirbelströmen im Substrat (Eddy Currents). Derzeit werden von keinem Hersteller parametrisierbare Modelle von Induktivitäten zur Verfügung gestellt. In manchen Fällen wurden lediglich einige Spulen implementiert und anschließend vermessen, wodurch die Freiheit beim Schaltungsdesign stark eingeschränkt ist [Hein04].

Nachfolgend wird der Einfluss des Substrats sowie die Grundlagen zum Aufbau von integrierten Induktivitäten aufgezeigt und erklärt. Anschließend wird der im Rahmen dieser Arbeit angefertigte Generator für integrierte Induktivitäten sowie die zur Simulation verwendeten Modelle näher erläutert.

#### 2.2.1 Aufbau integrierter Induktivitäten

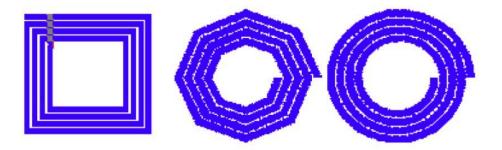

Die Ausführung einer Induktivität ist auf verschiedene Arten möglich und kann viereckig, oktagonal oder sogar hexagonal sein. Die größte Induktivität pro Fläche wird jedoch mit einer runden Realisierung erzielt. Aus fertigungstechnischen Gründen sind solche Spulen jedoch in vielen Prozessen nicht zugelassen.

Abbildung 2-2: Beispiele integrierter Induktivitäten

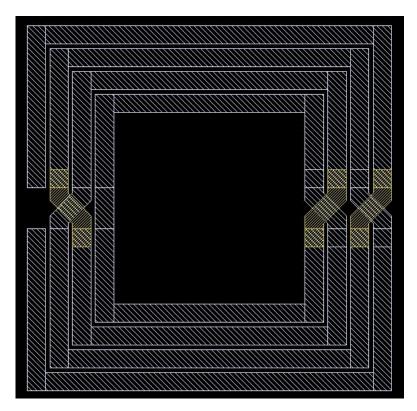

Das Layout einer Induktivität kann auch von der Art der Anwendung bestimmt sein. So ist beispielsweise für differentielle Schaltungen oft eine symmetrische Spule wünschenswert. In Abbildung 2-3 ist das automatisch generierte Layout einer symmetrischen spiralen Induktivität dargestellt.

Abbildung 2-3: Layout einer symmetrischen Induktivität

Um eine möglichst hohe Güte der Spule zu erreichen, werden in der Regel alle zur Verfügung stehenden Metall-Lagen genutzt. In einigen Fällen kann es von Vorteil sein, die unteren Metall-Lagen nicht zu verwenden. Auf diese Weise lässt sich der Abstand der Spule zum Substrat vergrößern. Daraus resultiert eine Abnahme der parasitären Kapazität.

#### 2.2.2 Physikalische Effekte

Im Folgenden werden die wichtigsten physikalischen Effekte beschrieben, die bei einer integrierten Spule auftreten und zu berücksichtigen sind.

#### 2.2.2.1 Eigenresonanz

Infolge der parasitären Kapazität zwischen dem Metall der Spule und dem Substrat verhält sich die Induktivität wie ein RC-Schwingkreis. Die Frequenz, bei der dieser Schwingkreis in Resonanz gerät,

wird Eigenresonanzfrequenz  $f_{res}$  der Spule genannt. Anhand der nachfolgenden Gleichung kann sie ermittelt werden

$$f_{res} = \frac{1}{2\pi\sqrt{LC}}. ag{2-4}$$

Hierbei ist L die Induktivität der Spule und C die parasitäre Kapazität zum Substrat. Oberhalb dieser Frequenz verhält sich die Spule wie eine Kapazität. Um eine starke Abnahme der Güte zu vermeiden, sollte die Frequenz, bei der die Spule zum Einsatz kommt, möglichst weit unterhalb der Resonanzfrequenz liegen [Pete03].

Um eine hohe Eigenresonanzfrequenz zu erzielen, muss die Kapazität, bei einem festen Wert L der Induktivität, möglichst gering sein. Dies kann durch einen großen Abstand zum Substrat oder eine kleine Fläche der Spule erreicht werden. Es ist zu beachten, dass eine kleine Fläche zunehmende ohmsche Verluste im Leiter zur Folge hat.

#### 2.2.2.2 Skin Effekt

Der Skin Effekt, auch Stromverdrängung genannt, gewinnt bei Induktivitäten an Einfluss, wenn diese im Gigahertzbereich betrieben werden. Der Effekt zeichnet sich dadurch aus, dass infolge des höherfrequenten Wechselstroms die Stromdichte im Inneren des Leiters niedriger ist als an der Oberfläche. Die Eindringtiefe d ist abhängig von der magnetischen Permeabilität  $\mu$ , dem spezifischen Widerstand des Materials  $\rho$  und der Frequenz f:

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}}.$$

(2-5)

Der Effekt ist durch den Schaltungsentwickler nur sehr beschränkt beeinflussbar. In verschiedenen Publikationen wird gezeigt, dass bei planaren Induktivitäten der Einfluss des Skin Effekts mit der Leiterbahnbreite ansteigt. Nach [Long97] liegt die optimale Leiterbahnbreite bzgl. des ohmschen Widerstands bei 15µm. Eine weitere Vergrößerung der Leiterbahnbreite führt nicht zu einer Verbesserung der Güte.

#### 2.2.2.3 Wirbelströme

In den Windungen einer Spule und im Substrat unter einer Spule können Ströme auftreten, die durch das Magnetfeld einer Induktivität verursacht werden. Diese Wirbelströme (eddy current) erzeugen ihrerseits ein Magnetfeld, welches bei hohen Frequenzen und großen Querschnitten den Strom aus der Mitte des Leiters verdrängt (Skin Effekt). Der Einfluss dieses Effekts auf die Güte der Spule ist größer als der des eigentlichen Skin Effekts.

Betrachtet man zunächst nur die induzierten Ströme im Substrat, so ist deren Einfluss auf die Induktivität vernachlässigbar klein, wenn es sich um ein Substrat mit niedriger Dotierung handelt. Bei niederohmigen Substraten nimmt der Einfluss dieses Effekts hingegen zu. Das durch die induzierten Substratströme entstandene Magnetfeld durchdringt den Leiter der Spule und ruft wiederum Ströme hervor, die dem ursprünglichen Strom entgegen gerichtet sind. Zur Ermittlung genauer Werte der Wirbelströme und deren Einfluss auf die Spule sind Simulationen mit Finiten Elementen durchzuführen, da eine direkte Berechnung nur sehr ungenau möglich ist. Anschaulich kann man sich die Ströme im Substrat und in der Induktivität auch wie in einem Übertrager vorstellen. Der ohmsche Widerstand im Substrat überträgt sich auf die Primärspule und verschlechtert auf diese Weise deren Güte. In der Mitte der Induktivität ist das Magnetfeld infolge der Überlagerung aller Anteile der Windungen am stärksten. Dies hat zur Folge, dass auch die Wirbelströme hier am größten sind und

damit sowohl auf den Wert der Induktivität, als auch auf den Wert des ohmschen Widerstands einer Spule den meisten Einfluss ausüben. Aus diesem Grund ist das Zentrum bei Induktivitäten mit einer hohen Güte nicht zu verwenden.

Eine Möglichkeit Wirbelströme im Substrat und die damit verbundenen ohmschen Verluste in der Spule zu vermeiden, besteht in der Verwendung einer Substratabschirmung. Es wird hierbei eine leitfähige Schicht aus Metall oder Polysilizium unter den Wicklungen der Spule aufgebracht. Auf diese Weise wird ein Eindringen des Magnetfeldes in das Substrat verhindert. Um Wirbelströme innerhalb des Schildes zu vermeiden, ist es notwendig, dieses rechtwinklig zu den Leitern der Spule mit Unterbrechungen (Schlitze) zu versehen. Nachteil der Ein bei Verwendung Substratabschirmungen ist die Zunahme des Kapazitätswertes unter der Spule, infolge des geringeren Abstands des unteren Leiters zur Abschirmung als zum Substrat. Eigenresonanzfrequenz der Spule wird auf diese Weise ebenfalls herabgesetzt. Aus diesem Grund ist bei Anwendungen, die beispielsweise eine sehr geringe parasitäre Kapazität der Spule benötigen, auf eine derartige Abschirmung zu verzichten.

#### 2.2.3 Modellierung

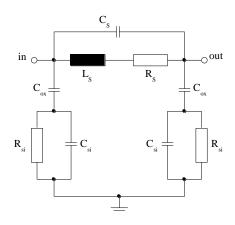

Um eine integrierte spiralförmige Induktivität in einer CMOS Technologie modellieren zu können, wird die Spule in rechteckige Segmente unterteilt. Zur Vereinfachung der Implementierung werden lediglich quadratische spiralförmige Spulen betrachtet. Eine Erweiterung auf andere Geometrien, wie beispielsweise oktagonale Spiralen, ist mit einem erhöhten Rechenaufwand möglich. Das Ersatzschaltbild, welches für jedes Segment angewandt wird, ist der Abbildung 2-4 zu entnehmen [Ashb94]. Neben der Reihenschaltung, bestehend aus der Induktivität L<sub>s</sub> und dem parasitären Leitungswiderstand R<sub>s</sub>, werden ebenfalls die Streukapazitäten zwischen den Leitungen (C<sub>s</sub>) und die Wechselwirkungen mit dem Substrat (C<sub>ox</sub>) berücksichtigt. Das ohmsche und das weitere kapazitive Verhalten des Substrats werden durch die Parallelschaltung von C<sub>si</sub> und R<sub>si</sub> beschrieben. Die Induktivität L<sub>s</sub> beinhaltet neben der Eigeninduktivität des jeweiligen Segments, die wechselseitige Induktivität zwischen den entsprechenden parallel verlaufenden Segmenten. Der Reihenwiderstand R<sub>s</sub> vergrößert sich mit steigender Frequenz infolge des Skin Effekts. Die folgende Gleichung ermöglicht eine Berechnung des Widerstands für die einzelnen Segmente der spiralförmigen Spule unter Berücksichtigung des genannten Effekts [Yue99]:

$$R_S = \frac{\rho L}{W\delta(1 - e^{-t_W/\delta})},\tag{2-6}$$

mit

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}}.$$

wobei  $\rho$  den spezifischen Widerstand des Materials, welches für Leitungen der spiralen Induktivität verwendet wird, beschreibt. Die Dicke der Leitung wird mit Hilfe von  $t_W$  spezifiziert, L ist die Länge des jeweiligen Segments, W ist die Breite der Leitung,  $\mu$  die Permeabilität des Leitungsmaterials und f die Frequenz, für die der Serienwiderstand berechnet werden soll.

Abbildung 2-4: Ersatzschaltbild der Spule

Die Kapazität Cox baut sich zwischen der untersten Maskenebene der spiralen Spule und dem Substrat auf. Der Wert für die Kapazität berechnet sich wie folgt:

$$C_{ox} = \frac{1}{2} \cdot L \cdot W \cdot \frac{\varepsilon_0 \cdot \varepsilon_{ox}}{t_{ox}},\tag{2-8}$$

dabei ist  $\epsilon_0$  die Dielektrizitätskonstante des Vakuums,  $\epsilon_{ox}$  die relative Dielektrizitätskonstante des Oxids zwischen der untersten Ebene der Spule und dem Substrat. Die Länge des jeweiligen Segments wird durch L angegeben, W beschreibt die Leitungsbreite und  $t_{ox}$  definiert den Abstand zwischen der Maskenebene und der Epitaxie-Schicht. Falls in der einzusetzenden Technologie keine Epitaxie-Schicht existiert, ist durch  $t_{ox}$  der Abstand zum Substrat gegeben.

Die hochfrequenten kapazitiven Effekte, die bei der integrierten spiralförmigen Spule auftreten können, werden durch die Kapazität  $C_{si}$  modelliert. Eine Einflussnahme durch die Leitfähigkeit des Substrats wird durch den Widerstand  $R_{si}$  berücksichtigt. Die Abmessungen einer spiralen Induktivität sind in der Regel deutlich größer als die Oxiddicke und damit eher vergleichbar mit der Dicke des Substrats. Aus diesem Grund verhalten sich die Werte der Substratkapazität und des Substratwiderstands näherungsweise proportional zur Fläche, die durch die Spule eingenommen wird. Damit können  $C_{si}$  und  $R_{si}$  mittels folgender Gleichungen approximiert werden:

$$C_{si} = \frac{1}{2} \cdot L \cdot W \cdot C_{substrat},\tag{2-9}$$

und

$$R_{si} = \frac{2 \cdot R_{substrat}}{L \cdot W},\tag{2-10}$$

wobei L die Länge des jeweiligen Segments der Spule darstellt und W die Leitungsbreite ist. Der Kapazitätswert des Substrats pro Flächeneinheit ist durch  $C_{\text{substrat}}$  gegeben, während  $R_{\text{substrat}}$  den Widerstand des Substrats pro Flächeneinheit beschreibt.

Die Berechnung der Werte der Induktivität selber ist deutlich aufwendiger. Wie eingangs bereits erwähnt wurde, ist neben der Eigeninduktivität die wechselseitige Induktivität zu parallel verlaufenden Segmenten der Spule für jeden Leitungsabschnitt zu berechnen. Nach [Yue00] kann die Eigeninduktivität eines rechteckförmigen Leitungssegments durch die nachfolgende Gleichung bestimmt werden:

$$M_0 = 2 \cdot L \cdot \left( \log \frac{2 \cdot L}{W + t_W} + \frac{W + t_W}{3 \cdot L} + \frac{1}{2} \right), \tag{2-11}$$

wobei L die Länge des Segments, W die Leitungsbreite und t die Dicke der Leitung definieren. Zur Berechnung der wechselseitigen Induktivität von parallel verlaufenden Leitungen ist die Abbildung 2-5 zu betrachten.

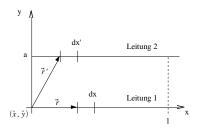

Abbildung 2-5: Wechselseitige Teilinduktivität von zwei parallel verlaufenden Leitungen

Hier bezeichnet a den Abstand zwischen den beiden Leitungen und I die Länge hinsichtlich der die beiden Segmente parallel verlaufen. Es gilt ferner:

$$\vec{r} = x \cdot \hat{x},\tag{2-12}$$

$$\vec{r}' = x' \cdot \hat{x} + a \cdot \hat{y},\tag{2-13}$$

$$|\vec{r}' - \vec{r}| = \sqrt{(x' - x)^2 + a^2}.$$

(2-14)

Damit ergibt sich für die wechselseitige Teilinduktivität:

$$M = \int_0^l \int_0^l \frac{dx \cdot dx'}{\sqrt{(x'-x)^2 + a^2}} = 2 \cdot l \cdot \left[ \log \left( \frac{l}{a} + \sqrt{1 + \left( \frac{l}{a} \right)^2} \right) - \sqrt{1 + \left( \frac{l}{a} \right)^2} + \frac{a}{l} \right]. \tag{2-15}$$

Um aus der resultierenden Teilinduktivität die tatsächliche wechselseitige Induktivität zwischen den parallel verlaufenden Leitungen zu ermitteln, ist die Distanz a durch den mittleren geometrischen Abstand GMD zu ersetzen [Hoer65, Gree74]. Ein hinreichend genauer Ausdruck zur Berechnung dieses Wertes ist durch die folgende Gleichung gegeben:

$$\log GMD = \log d - \frac{w^2}{12d^2} - \frac{w^4}{60d^4} - \frac{w^6}{168d^6} - \frac{w^8}{360d^8} - \frac{w^{10}}{660d^{10}}.$$

(2-16)

wobei d die Distanz zwischen den Leitungen und w die Leitungsbreite angeben.

Basierend auf Grovers Formeln [Grov62] entwickelte Greenhouse einen Algorithmus zur Berechnung von ebenen rechtwinkeligen Spiralen [Gree74]. Diese Methode zeigt, dass die Gesamtinduktivität einer spiralförmigen Spule dadurch berechnet werden kann, dass die Eigeninduktivität jedes Leitungssegments sowie die wechselseitigen Induktivitäten zwischen den entsprechenden Segmenten aufsummiert wird. Die wechselseitige Induktivität hängt dabei vom Winkel der Segmente zueinander, deren Länge und dem Abstand ab. Orthogonal verlaufende Segmente weisen dabei keine Kopplung auf, da zwischen diesen kein magnetischer Induktionsfluss besteht.

Für die Auswertung der Gesamtinduktivität einer quadratischen Spirale mit N Windungen sind 4N Terme für die Eigeninduktivität, 2N(N-1) positive und 2N<sup>2</sup> negative Terme für die wechselseitige Induktivität zu berechnen. Alle geraden Segmente einer spiralförmigen Spule seien durchnummeriert

von 1 bis N. Die Gesamtanzahl der Segmente ist damit durch N gegeben. Die Nummerierung erfolgt von außen nach innen. Damit lässt die Induktivität der Spule nach Algorithmus 2-1 berechnen.

Algorithmus 2-1: Berechnung der Induktivität einer Spule

```

M_0:=Summe der Eigeninduktivitäten der Segmente s_i mit s_i \in S und 1 \le i \le N;

M^{-} := 0;

für i:=1 bis N-2

für j:=1 bis n

k := i + 4 * j - 2;

wenn k≤N dann

Mik:=wechselseitige Induktivität zwischen Segment si und sk;

M^{-} := M^{-} + M_{ik};

wenn ende

für ende

für ende

M^{-} := M^{-} * 2;

M^{+} := 0;

für i:=1 bis N-2

für j:=1 bis n

k := i + 4 * j;

wenn k \le N dann

M_{ik}:=wechselseitige Induktivität zwischen Segment s_i und s_k;

M^{+} := M^{+} + M_{ik};

wenn ende

für ende

für ende

M^{+} : = M^{+} * 2

L := M_0 + (M^+ - M^-) :

```

#### 2.2.4 Modulgenerator zur Erstellung von symmetrischen Induktivitäten

In diesem Abschnitt wird ein Generator zur automatischen Erstellung des Layouts einer integrierten symmetrischen spiralförmigen Induktivität beschrieben. Die MOGLAN Bibliothek dient als Grundlage für den Generator. Dadurch ist ferner eine Unabhängigkeit von der zu verwendenden Technologie gewährleistet. Als Parameter besitzt dieses Modul die Anzahl der Windungen der Spule, die Breite der Leitung und die Innenweite der Spule. Innerhalb dieses Gebiets werden keine Windungen erstellt. Weiterhin kann die Maskenebene vom Benutzer ausgewählt werden, die für die Erstellung der Leitungen verwendet wird. Um die Spule auch bei einer Postlayout-Simulation mit zu berücksichtigen, ist es möglich eine Spectre-Beschreibung durch den Generator erstellen zu lassen. Dazu werden das im Abschnitt "Modellierung" beschriebene Ersatzschaltbild und die entsprechenden Gleichungen umgesetzt. Für die erfolgreiche Modellierung der Simulationsdaten sind durch den Benutzer Angaben zum Flächenwiderstand des Leitungsmaterials, zu der Dicke der Epitaxie-Schicht, zu dem Abstand zwischen der Epitaxie-Schicht und der Leitungsebene sowie zur Dielektrizitätskonstante des Oxids zu machen. Falls die zu benutzende Technologie über keine Epitaxie-Schicht verfügt, sind die entsprechenden Werte für das Substrat zu wählen.

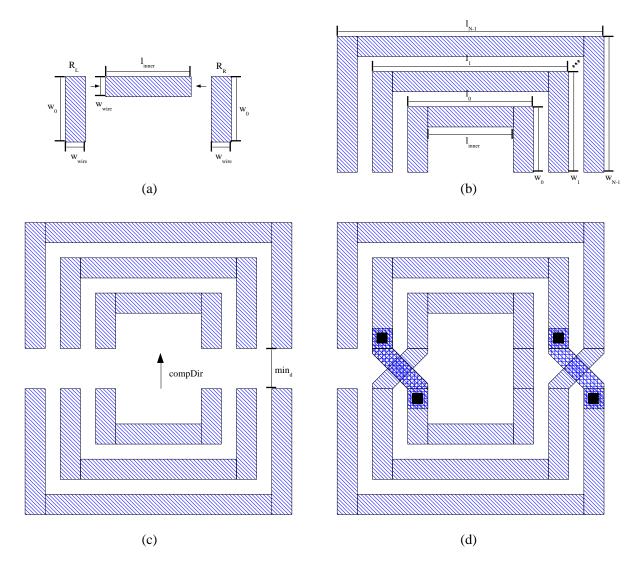

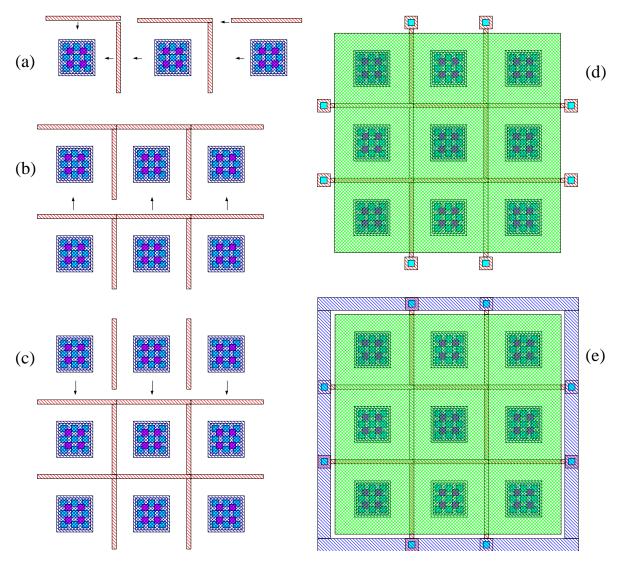

Abbildung 2-6: Abfolge zur Erstellung einer symmetrischen spiralen Induktivität

Der Ablauf der Konstruktion des Layouts einer symmetrischen spiralförmigen Induktivität in einer CMOS Technologie ist in Abbildung 2-6 dargestellt. Der erste Schritt beschreibt die Erstellung von Teilwindungen, bestehend aus je drei Rechtecken (siehe Abbildung 2-6 (a)), die aneinander kompaktiert werden. Der Vorgang wird N-mal durchgeführt, wobei N die Anzahl der Windungen der Spule definiert. Die Größen  $w_{wire}$  und  $l_{inner}$  werden durch den Benutzer vorgegeben und spezifizieren die Leitungsbreite bzw. die Innenweite der spiralen Induktivität. Die Abmessung  $w_0$  der Rechtecke  $R_L$  und  $R_R$  errechnet sich wie folgt:

$$w_0 = w_{wire} + \frac{1}{2} \cdot (l_{inner} - (min_d + 2 \cdot w_{wire})), \tag{2-17}$$

wobei

$$min_d = minDist(Layer_{ind}) + 2 \cdot w_{wire},$$

(2-18)

den Abstand zwischen den beiden Mengen der Teilwindungen darstellt (siehe Abbildung 2-6 (c)). Der Ausdruck minDist(Layer<sub>ind</sub>) beschreibt die durch die Technologie vorgegebene Mindestdistanz zwischen Strukturen, die mit Hilfe der Maske Layer<sub>ind</sub> gefertigt werden. Iterativ werden nun die Teilwindungen der Spule erstellt (siehe Abbildung 2-6 (c)). Die jeweils neuen Abmessungen können rekursiv berechnet werden. Es ist

$$w_i = w_{i-1} + w_{wire} + minDist(Layer_{ind}), (2-19)$$

$$l_i = l_{i-1} + 2 \cdot (minDist(Layer_{ind}) + w_{wire}), \tag{2-20}$$

wobei  $w_0$  durch Gl. (2-17) gegeben ist und für  $l_0$  gilt:

$$l_0 = l_{inner} + 2 \cdot w_{wire}. \tag{2-21}$$

Auf diese Weise entstehen zwei Strukturen mit N Teilwindungen, die im nächsten Schritt aneinander kompaktiert werden (siehe Abbildung 2-6 (c)), wobei ein Mindestabstand von min<sub>d</sub> (siehe Gl. (2-18)) eingehalten wird. Abschließend erfolgt eine kreuzweise Verbindung der entsprechenden Leitungen (siehe Abbildung 2-6 (d)). Das resultierende Layout einer integrierten Induktivität nach erfolgreicher Ausführung des Generators ist der Abbildung 2-3 zu entnehmen.

Es ist das Layout für verschiedene Induktivitäten in einer 025µm CMOS Technologie der Firma IHP GmbH angefertigt worden. Die nachfolgende Tabelle 2-1 zeigt die Ergebnisse des Generators zur Berechnung der Gesamtinduktivität der jeweiligen Spulen. Um einen Vergleich zu den tatsächlichen Werten zu haben, sind die Meßergebnisse der Spulen ebenfalls in die Tabelle mit aufgenommen worden. Die Messwerte sind den Angaben der Firma IHP GmbH entnommen worden.

Tabelle 2-1: Vergleich zwischen Simulationswerten und Messwerten für verschiedene Induktivitäten

|                  |                 | Induktivität [nH]   |                 |           |

|------------------|-----------------|---------------------|-----------------|-----------|

| Anzahl Windungen | Innenweite [µm] | Leitungsbreite [µm] | Laut Hersteller | Generator |

| 7                | 159             | 7.98                | 11.7            | 11.69     |

| 8                | 109.6           | 6.99                | 14.7            | 13.63     |

| 8                | 176.4           | 7.98                | 23.8            | 21.04     |

#### 2.3 Widerstände

Grundlegend stehen in den Technologien vier verschiedene Arten von Widerständen zur Verfügung:

- Diffusionswiderstand

- Polysiliziumwiderstand

- Wannenwiderstand

- Filmwiderstand

Zur Erzeugung von Diffusionswiderständen werden spezielle Strukturen geformt, wie sie auch für die Erstellung von Transistor-Diffusionsgebieten genutzt werden. Es entsteht ein sogenannter Volumenwiderstand, der sich aus der Länge, Weite und Tiefe der Dotierschicht ergibt. Polysiliziumwiderstände nutzen den ohmschen Widerstand der Polyschicht aus. Sie können mittels Maskenformen auch mäanderförmig strukturiert werden. Infolge einer derartigen Strukturierung sind sehr große Widerstandswerte realisierbar. Beim vergrabenen Widerstand bildet eine relativ leicht dotierte Wanne im Substrat den Widerstandskörper [Gray93]. Die Herstellung von Dünnfilm-Widerständen setzt zusätzliche Prozess-Schritte voraus. Diese Schritte bedingen eine Sondertechnologie, so dass sie üblicherweise nicht für CMOS-Prozesse zur Verfügung steht. Bei dieser Art von Widerständen werden dünne Schichten von Tantal oder Nickel-Chrom-Verbindungen auf dem Wafer aufgebracht [Gray93].

#### 2.3.1 Genauigkeit integrierter Widerstände

In diesem Abschnitt werden die Absolutgenauigkeit sowie die Paarungsgenauigkeit von integrierten Widerständen näher untersucht. Zu diesem Zweck ist im Folgenden ein rechteckförmiger Widerstand

zu betrachten. Weiterhin sei der Widerstand der Kontaktierungen als vernachlässigbar anzusehen. Der Widerstandswert berechnet sich wie folgt:

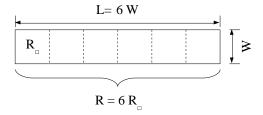

$$R = \frac{\overline{\rho}}{\overline{x_I}} \cdot \frac{L}{W} = R_{\square} \cdot \frac{L}{W}. \tag{2-22}$$

wobei  $\bar{\rho}$  den mittleren spezifischen Widerstand, L und W die Abmessungen des Widerstands und  $x_j$  die durchschnittliche Dicke der zu betrachtenden Struktur beschreiben. Der Flächen-Widerstand (Square-Widerstand)  $R_{\Box}$  ist lediglich von den Prozessparametern abhängig, wenn die Weite W und die Länge L identisch sind. Generell werden Widerstände als Vielfaches des Squarewiderstands aufgefasst (siehe Abbildung 2-7).

Abbildung 2-7: Berechnung des Widerstandswertes mit Hilfe des Flächenwiderstands

Häufig werden bei der praktischen Umsetzung integrierter Widerstände Strukturen mit einer Länge verwendet, die deutlich größer als die Weite ist, da in der Regel Widerstände benötigt werden, deren Wert über dem spezifischen Widerstandswert liegt. Eine Beeinflussung der Genauigkeit durch die Länge im Vergleich zur Weite ist in diesen Fällen vernachlässigbar. Insgesamt ist die Präzision der geometrischen Parameter abhängig von der Genauigkeit der Photolithographie, dem Ätzverfahren und der lateralen Ausdiffusion.

Abbildung 2-8: Beispiel zur Untersuchung der Paarungsgenauigkeit integrierter Widerstände

Ferner wird die Absolutgenauigkeit von Widerständen beeinträchtigt durch die Parameter der Prozessführung. So nehmen die voneinander unabhängigen Größen wie der Diffusionskonzentration, der Implationsdosis, der Diffusionstemperatur und der Diffusionszeit Einfluss auf die Genauigkeit. Die genannten Werte spiegeln sich in dem spezifischen Widerstandswert und der Dicke des Widerstands wider und können durch den Designer nicht direkt beeinflusst werden. Die daraus resultierenden Toleranzen können in einem Bereich von ca. 5% bis hin zu 20% auftreten. Der Absolutwert eines

Widerstands ist aus diesem Grund mit einer relativ hohen Ungenauigkeit behaftet. Hinsichtlich der Frage wie genau ein bestimmtes Widerstandsverhältnis hergestellt werden kann, ist im weiteren Verlauf die Abbildung 2-8 zu betrachten.

Es sind zwei Widerstände mit einem Verhältnis von (Abbildung 2-8 (a)) und deren mögliche Realisierungsform (Abbildung 2-8 (b)) dargestellt. Es gilt:

$$\frac{R_1}{R_2} = \frac{\overline{\rho}_1 \cdot \bar{x}_{j2}}{\overline{\rho}_2 \cdot \bar{x}_{j1}} \cdot \frac{L_1 \cdot W_2}{L_2 \cdot W_1} \approx \frac{L_1 \cdot W_2}{L_2 \cdot W_1},$$

(2-23)

wobei

$$\frac{\overline{\rho}_1 \cdot \overline{x}_{j_2}}{\overline{\rho}_2 \cdot \overline{x}_{j_1}} \tag{2-24}$$

vom Prozess abhängig ist und

$$\frac{L_1 \cdot W_2}{L_2 \cdot W_1}$$

(2-25)

durch das Layout beeinflusst wird. Falls die Widerstände mit denselben Prozess-Schritten zeitgleich gefertigt werden und eine enge räumliche Nähe zueinander aufweisen, so heben sich die aus der Prozessfolge resultierenden Toleranzen weitestgehend auf. Die Paarungsgenauigkeit ist daher vom Layout abhängig. Die Wahl geeigneter Layoutstrukturen liefert eine Toleranzgrenze von besser als 1‰.

#### 2.3.2 Einfluss der Temperatur

Die Ausrichtung von hochpräzisen Bauelementen im Hinblick auf wärmeproduzierende Schaltungsbereiche ist bei den integrierten Schaltungen ebenfalls von Bedeutung. So sind Transistoren und Widerstände temperaturabhängige Komponenten. Um eine Beeinflussung der Genauigkeit durch einen Temperaturgradienten zu minimieren, sollten die betroffenen Elemente symmetrisch zu den Wärmequellen ausgerichtet werden.

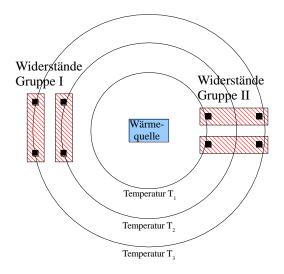

Abbildung 2-9: Ausrichtung von Widerständen zu einer Wärmequelle

Die in Abbildung 2-9 gezeigten Widerstände der Gruppe I werden eine Diskrepanz aufweisen, da beide Widerstände unterschiedlichen Temperaturbereichen ausgesetzt sind. Demgegenüber sind die Widerstände der Gruppe II symmetrisch bzgl. der Temperaturzonen ausgerichtet, so dass Paarungsfehler bedingt durch Temperatureinflüsse in diesem Fall nahezu ausgeschlossen werden können.

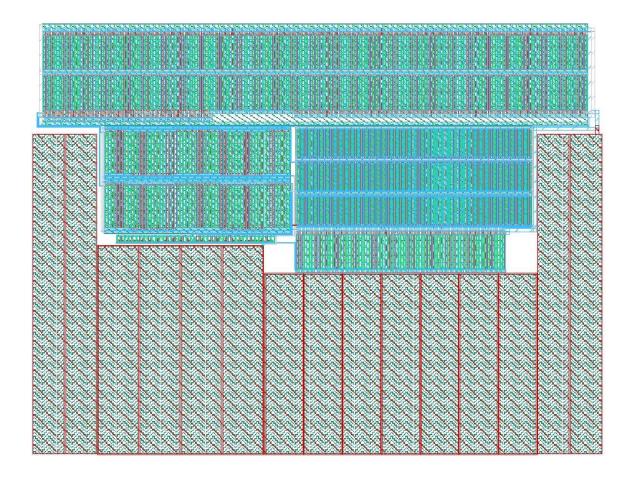

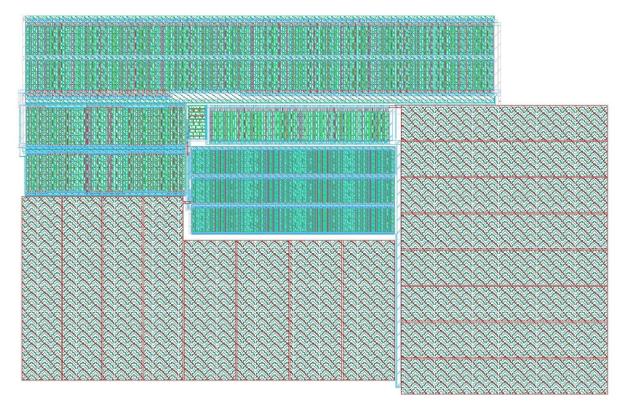

#### 2.3.3 Modulgenerator zur Erstellung von Präzisionswiderständen

In diesem Abschnitt wird die Funktionsweise des Modulgenerators zur Erstellung von Präzisionswiderständen [Zhan09] anhand von ausgewählten Beispielen beschrieben. Für die Generierung sind die Eingabe der Länge und der Weite eines einzelnen Widerstandssteifens, die Anzahl der gewünschten Zeilen und das Verhältnis der Widerstände innerhalb der Präzisionswiderstandsstruktur erforderlich. Die Gesamtanzahl an Widerstandsstreifen ermittelt der Generator automatisch mittels der Verhältnisangabe der Widerstände. Nach erfolgreicher Ausführung ergibt sich beispielsweise das in Abbildung 2-10 gezeigte Layout eines Präzisionswiderstands.

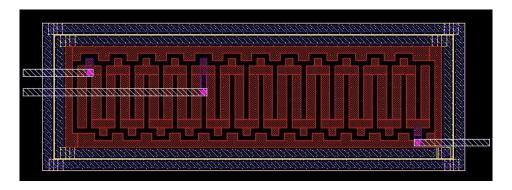

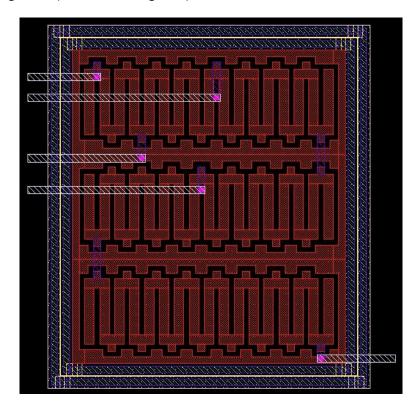

Abbildung 2-10: Layout eines Präzisionswiderstands

Die Anschlüsse der jeweiligen Widerstände werden zu einer Seite des Moduls herausgeführt. Die Verbindungen innerhalb der Widerstandsstruktur werden bei mehrzeiligen Präzisionswiderständen selbsttätig durchgeführt (siehe Abbildung 2-11).

Abbildung 2-11: Layout eines mehrzeiligen Präzisionswiderstands

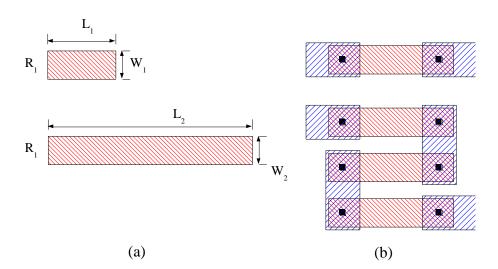

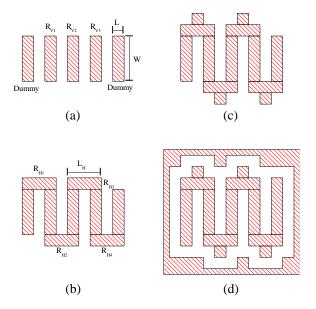

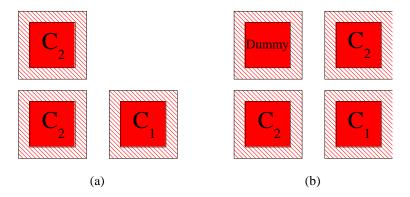

Im Folgenden wird die Generierung einer Zeile eines Präzisionswiderstands näher erläutert. Die Generierung für drei Widerstandsstreifen und den entsprechenden Dummy-Strukturen ist in Abbildung 2-12 dargestellt.

Abbildung 2-12: Abfolge zur Generierung eines Präzisionswiderstands

Der erste Schritt beinhaltet eine Kompaktierung der Widerstandsstreifen in horizontaler Richtung (Abbildung 2-12 (a)). Die jeweiligen Streifen weisen die vom Benutzer vorgegebene horizontale Länge L und die vertikale Weite W auf. Der minimale Abstand zwischen den Streifen ist durch die zu verwendende Technologie vorgegeben und wird durch den Generator automatisch berücksichtigt. Der erste und der letzte Widerstandsstreifen stellen die Dummy-Elemente dar, während die verbleibenden Elemente die aktiven Widerstände darstellen. Im anschließenden Schritt werden durch eine vertikale Kompaktierung von horizontal verlaufenden Rechtecken die einzelnen Widerstandsstreifen miteinander verbunden (Abbildung 2-12 (b)). Die Größe der herankompaktierten Rechtecke berechnet sich in horizontaler Richtung wie folgt:

$$L_H = 2 \cdot L + \Delta_{min}. \tag{2-26}$$

wobei  $\Delta_{min}$  den Mindestabstand zwischen den vertikalen Streifen bezeichnet. Die Weite der horizontalen Streifen beträgt W. Auf jedem der horizontalen Verbindungselemente wird ein kleines Rechteck zentriert herankompaktiert (Abbildung 2-12 (c)), um auf diese Weise eine Anschlussmöglichkeit für spätere Metall-Leitungen zu ermöglichen. Im letzten Schritt wird die Umgebung des Präzisionswiderstands, bestehend aus entsprechenden Dummy-Elementen, erzeugt (Abbildung 2-12 (d)). Um eine hinreichend große Paarungsgenauigkeit der einzelnen Widerstände zueinander zu erzielen, ist auf einen gleichmäßigen Abstand zwischen dem Widerstand und der Dummy-Struktur zu achten.

Falls die Anzahl an Zeilen für den Präzisionswiderstand größer als eins ist, wird für jede Zeile eine Grundstruktur nach der beschriebenen Vorgehensweise erstellt. Es wird dabei jede generierte Grundstruktur in vertikaler Richtung an die vorhergehende Widerstandszeile herankompaktiert, wobei diejenigen Strukturen mit einer geraden Zeilennummer zuvor an der x-Achse gespiegelt werden. Anschließend erfolgt eine Verbindung mit Hilfe von Metall-Leitungen von denjenigen Widerständen, die sich über mehr als eine Zeile ausdehnen. Zur Entkopplung zum Substrat, werden

um die erstellte Widerstandsstruktur abschließend zwei Guardringe platziert. Es werden weiterhin die notwendigen Anschlüsse der Widerstände innerhalb der Struktur mit Hilfe von Metall-Leitungen an den Rand des Moduls herausgeführt. Das resultierende Ergebnis für einen einzeiligen bzw. einen mehrzeiligen Präzisionswiderstand ist in Abbildung 2-10 bzw. in Abbildung 2-11 dargestellt.

#### 2.4 Kapazitäten

In Abhängigkeit von der jeweiligen Prozesstechnologie lassen sich grundsätzlich verschiedene Realisierungen für integrierte Kondensatoren beschreiben. Derartige Kondensatorstrukturen sind für analoge und Mixed-Signal Schaltungen oft unerlässlich, auch wenn nur verhältnismäßig kleine Kapazitätswerte realisiert werden können. Ein einfacher Kondensator bildet sich durch die Isolation (SiO2) zwischen einer Polysilizium- und einer Metallebene. Stehen in einer Technologie mehrere Polyebenen zur Verfügung, so kann auch mit Hilfe einer Isolationsschicht zwischen zwei Polyebenen ein Kondensator erstellt werden [Alle87]. Eine dritte Möglichkeit ist Verwendung einer Epitaxieschicht als Gegenelektrode zu einer Poly- oder Metallbahn. Ebenfalls ist eine Struktur realisierbar, die zwischen den Metallisierungsebenen angeordnet ist. Abschließend ist es ebenfalls sinnvoll alle Leiterbahnen miteinander zu verknüpfen, so dass bei gleicher Fläche nahezu eine Verdopplung des Kapazitätswertes erzielt werden kann.

#### 2.4.1 Genauigkeit integrierter Kapazitäten

Alle Prozessparameter bei Herstellung integrierter Schaltungen unterliegen einer lokalen Variation. Diese Streuung ist zufällig über die gesamte Chipfläche verteilt und kann nicht vorherbestimmt werden. So variiert bei der Fabrikation einer integrierten Kapazität die Oxiddicke und infolge von Über- bzw. Unterätzen kommt es zu einer zufallsbedingten Änderung an den Kanten. Aus diesen beiden Faktoren ergibt sich eine Abweichung des Kapazitätswertes von dem nominellen Wert der im Layout gezeichneten Geometrien. Eine wirksame Methode diesen lokalen Prozessfehlern entgegenzuwirken besteht nach [McCr81] darin, die betroffenen Elemente so groß zu wählen, dass die genannten Effekte lediglich eine untergeordnete Rolle spielen.

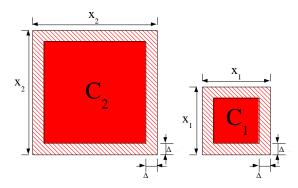

Die weiteren Möglichkeiten den Einfluss der negativen Effekte zu minimieren sollen im Folgenden näher untersucht werden. Dazu sind die in Abbildung 2-13 gegebenen beiden quadratischen Kapazitäten zu betrachten, deren Kapazitätsverhältnis zueinander K<sub>d</sub> betrage.

Abbildung 2-13: Beispiel zur Untersuchung der Paarungsgenauigkeit zweier quadratischer Kapazitäten

Durch die Wahl geeigneter Werte für  $x_1$  und  $x_2$  wird das zu erzielende Kapazitätsverhältnis im Layout eingestellt. Es gilt damit:

$$K_d = \frac{x_2^2}{x_1^2}. (2-27)$$

Falls es bei den Kapazitäten zu einer Über- oder Unterätzung in der Größenordnung  $\Delta x$  kommt, errechnet sich das reale Verhältnis wie folgt:

$$K_r = \frac{(x_2 - \Delta x)^2}{(x_1 - \Delta x)^2}. (2-28)$$

Der relative Fehler lässt sich dadurch berechnen nach:

$$err_K = \frac{K_d - K_r}{K_d} \approx \frac{2\Delta x}{x_2} \cdot \left(\sqrt{K_d} - 2\right).$$

(2-29)

Angenommen die Kapazität  $C_1$  weist die Dimensionen  $30\mu m \times 30\mu m$  auf und die Abweichungen an den Kanten beträgt  $\Delta x \approx 0.1\mu m$ . Für ein Kapazitätsverhältnis der Kapazitäten  $C_1$  und  $C_2$  von 1:4 ergibt sich damit nach GI. (2-29) ein Fehler von err<sub>K</sub>=0,66%. Bei einer Anwendung der beschriebenen Kapazitäten in einem A/D- bzw. D/A- Umsetzer könnte der Fehler zu einer Abweichung von  $\pm 0,5$  Bit führen. Damit ist es offensichtlich, dass die Kapazitäten in der dargestellten Form nicht für den Entwurf hochgenauer Schaltungen geeignet sind. Eine Reduzierung des Fehlers ist durch die Verwendung von Einheitskapazitäten gegeben (siehe Abbildung 2-14 (a)). In diesem Fall werden die Flächen der Kapazitäten um den gleichen Faktor reduziert, das Verhältnis zwischen den jeweiligen Kapazitäten bleibt jedoch unverändert.

Abbildung 2-14: Verwendung von Einheitskapazitäten zur Einstellung eines Verhältnisses von 1:2

Es ist zu berücksichtigen, dass die Oxiddicke an unterschiedlichen Stellen des Wafers bzw. des Chips variiert. Im Hinblick auf die Paarungsgenauigkeit würde die Vernachlässigung dieses Gradienten bei der Verwendung von Einheitskapazitäten zu einer signifikanten Abweichung führen. Eine Verbesserung der Paarungsgenauigkeit kann in diesem Fall durch die Anwendung des Prinzips des gemeinsamen Schwerpunkts, d.h. eine konzentrische Anordnung der jeweiligen Einheitskapazitäten, erzielt werden (siehe Abbildung 2-14 (b)). Dabei ist auf eine dichte Platzierung der benachbarten Bauelemente zueinander zu achten.

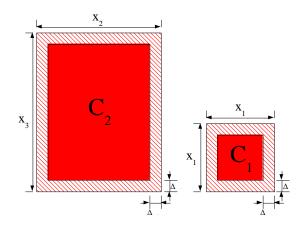

Die Benutzung von Einheitskapazitäten ist nur dann möglich, wenn die Werte der Kapazitäten durcheinander teilbar sind. Andernfalls sind rechteckförmige Kapazitäten zu verwenden. In diesem Fall ist jedoch eine Abhängigkeit der Paarungsgenauigkeit gegenüber lithographischen Streuungen und dem Ätzprozess gegeben. Die Einflussnahme der Fehler kann mit Hilfe einer geeigneten geometrischen Dimensionierung reduziert werden.

Abbildung 2-15: Beispiel zur Untersuchung der Paarungsgenauigkeit rechteckiger Kapazitäten

Das Verhältnis der in Abbildung 2-15 gezeigten Kapazitäten beträgt:

$$K_d = \frac{x_2 \cdot x_3}{x_1^2}. (2-30)$$

Infolge von Abweichungen durch das Ätzen ergibt sich das nachfolgende reale Verhältnis:

$$K_r = \frac{(x_2 - \Delta x) \cdot (x_3 - \Delta x)}{(x_1 - \Delta x)^2}.$$

(2-31)

Für den relativen Fehler gilt damit:

$$err_K \approx \frac{2\Delta x}{x_2^2} \cdot K_d \cdot \left(2x_1 - \frac{x_1^2(x_2 + x_3)}{x_2 x_3}\right).$$

(2-32)

Es werden nun Werte für  $x_2$  und  $x_3$  gesucht, so dass der relative Fehler err<sub>K</sub> bzgl.  $\Delta x$  minimiert wird. Dazu ist die erste Ableitung von err<sub>K</sub> in Abhängigkeit von  $\Delta x$  zu bestimmen und gleich Null zu setzen. Es ist:

$$0 = \frac{\delta err_K}{\delta \Delta x} = \frac{2x_2 x_3}{x_2^2 x_1^2} \cdot \left(2x_1 - \frac{x_1^2 (x_2 + x_3)}{x_2 x_3}\right) = \frac{2x_1}{x_2 + x_3} - \frac{x_1^2}{x_2 x_3}.$$

(2-33)

Der Term  $2x_1/(x_2+x_3)$  beschreibt das Umfangsverhältnis der beiden Kapazitäten, während der Term  $x_1^2/(x_2x_3)$  das Flächenverhältnis repräsentiert. Damit Gl. (2-33) erfüllt ist, muss das Umfangsverhältnis dem Flächenverhältnis entsprechen. Das Auflösen der Gl. (2-33) zur Bestimmung der optimalen Dimensionierung liefert:

$$x_2^2 - 2K_d x_2 + K_d = 0 (2-34)$$

und damit gilt

$$x_2 = K_d \pm \sqrt{K_d(K_d - 1)}. (2-35)$$

Eine Einschränkung ist aus Gl. (2-35) ersichtlich. Um eine verwertbare Lösung zu erhalten, ist für  $K_d$  ein Verhältnis größer als Eins zu wählen. Das bedeutet, dass die kleinste Kapazität als quadratische Einheitskapazität geformt werden sollte.

#### 2.4.2 Modulgenerator zur Erstellung eines binären Kapazitätsfeldes

Zur Erstellung eines binären Kapazitätsfeldes wird im ersten Schritt des Modulgenerators eine quadratische Einheitskapazität generiert. Die Abmessungen und die Masken, die zur Konstruktion der Kapazitäten verwendet werden, sind durch den Benutzer frei wählbar. Bei den Abmessungen wird von Seiten des Generators auf eine automatische Einhaltung der Design-Regeln geachtet. Auf diese Weise können beispielsweise Poly-Poly, Poly-Diffusion oder Metall-Metall Kapazitäten erzeugt werden. Der Aufbau ist dennoch gewissen Einschränkungen unterlegen, da sich nicht alle Realisierungsformen für die Kapazitäten im Hinblick auf die zu verwendenden Masken in jeder Technologie umsetzen lassen.

Aufgrund der Tatsache, dass das Ätzen bei der Herstellung nicht zu vernachlässigende Problem mit sich bringen kann, insbesondere in Bezug auf die Ecken der Kapazitäten, werden diese bei der oberen Maske mit 45° Kanten versehen. Um eine Verbindung mit später Verdrahtung zu ermöglichen, wird in der Mitte der Einheitskapazität ein Kontakt erstellt. Zur Gewährleistung einer einheitlichen Umgebung für jede Einheitskapazität, werden um das Feld der Kapazitäten Dummy-Strukturen aufgebaut. Die Verbindung der unteren Elektrode der Kapazitäten erfolgt in dem Material der angegebenen Maske, während die oberen Elektroden unter Verwendung von Metall-Leitungen zusammengeschlossen werden.

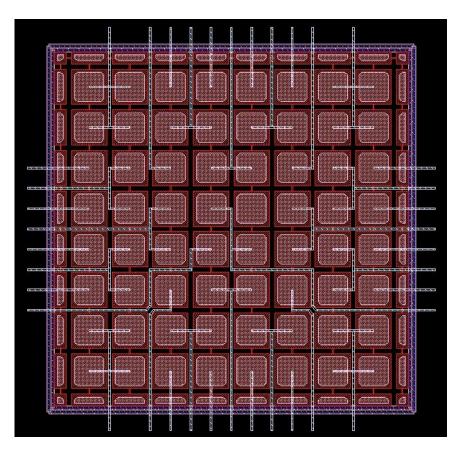

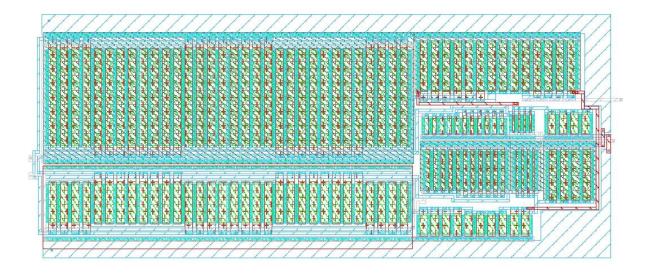

Abbildung 2-16: Automatisch generiertes Layout eines 6-Bit Kapazitätsfeldes

Insgesamt kann ein binäres Kapazitätsfeld für 2N Kapazitätsanteile (1≤N≤6) generiert werden. Die 1-Bit Kapazität befindet sich im Zentrum des Moduls. Die nachfolgenden Kapazitätsanteile werden aufsteigend hinsichtlich des Bit-Wertes konzentrisch um die 1-Bit Kapazität angeordnet. Auf diese Weise wird die mögliche Einflussnahme durch Schwankungen der Oxid-dicke und einer resultierenden Paarungsungenauigkeit mit berücksichtigt. Um ferner den Abstand zwischen den

Kapazitäten minimal zu halten, ist der Verlauf von maximal einer Leitung zwischen den Einheitskapazitäten erlaubt. Weiterhin ist es nicht gestattet, Leitungen über die Kapazitäten zu verlegen und es darf zu keiner Kreuzung von Verbindungen verschiedener Kapazitätsanteile innerhalb des Moduls kommen. Mit diesen Maßnahmen soll der Einfluss von Streukapazitäten auf die Paarungsgenauigkeit minimiert werden. Unter diesen Vorgaben können lediglich die 1- und die 2-Bit Kapazitäten innerhalb des binären Kapazitätsfeldes vollständig verdrahtet werden. Eine kreuzungsfreie Verbindung der Kapazitäten für 3- bis 6-Bit ist innerhalb des Feldes nicht möglich, so dass die Leitungen der Teilfelder nach außen geführt werden. Der Abbildung 2-16 ist das fertige Layout eines 6-Bit Kapazitätsfeldes zu entnehmen. Zur Reduzierung von Störeinflüssen aus dem Substrat sind zwei Guardringe um das binäre Kapazitätsfeld automatisch erstellt worden.

#### 2.4.3 Modulgenerator zur Erstellung von gepaarten Kapazitäten

Der im Nachfolgenden beschriebene Modulgenerator ermöglicht die Konstruktion gepaarter Kapazitäten, die nicht mit einem binären Kapazitätsfeld, bestehend aus einer angemessenen Anzahl an Einheitskapazitäten, erstellt werden können. Als Eingabeparameter stehen die Anzahl der Kapazitäten und eine Liste der korrespondierenden Kapazitätswerte zur Verfügung. Aus dieser durch den Nutzer vorgegebenen Liste der Kapazitätswerte  $C_1...C_n$  wird vor der Generierung des Moduls das Minimum ermittelt. Dieser im Folgenden als  $C_{min}$  bezeichnete Wert dient zum einen zum Aufbau der quadratischen Einheitskapazität, die mit Hilfe dieses Kapazitätswertes erstellt wird, zum anderen wird damit das Verhältnis zu den verbleibenden Kapazitätswerten berechnet. Ohne Beschränkung der Allgemeinheit sei im Folgenden  $C_i = C_{min}$ , dann gilt:

$$\eta_{1} = \frac{C_{1}}{C_{min}}$$

$$\vdots$$

$$\eta_{i-1} = \frac{C_{i-1}}{C_{min}}$$

$$\eta_{i} = 1$$

$$\eta_{i+1} = \frac{C_{i+1}}{C_{min}}$$

$$\vdots$$

$$\eta_{n} = \frac{C_{n}}{C_{min}}$$

Die Abmessungen der quadratischen Einheitskapazität berechnen sich unter Verwendung des Kapazitätswertes  $C_{\text{sheet}}$ , der den Kapazitätsbelag pro Flächeneinheit in Abhängigkeit von der einzusetzenden Technologie beschreibt, wie folgt:

$$L_{min} = W_{min} = \sqrt{\frac{c_{min}}{c_{sheet}}}. (2-37)$$

Die Länge und die Breite der verbleibenden Kapazitäten werden durch die nachstehenden Funktionen berechnet:

$$L_{1} = L_{min} \cdot \left(\eta_{1} - \sqrt{\eta_{1}^{2} - \eta_{1}}\right)$$

$$W_{1} = W_{min} \cdot \left(\eta_{1} + \sqrt{\eta_{1}^{2} - \eta_{1}}\right)$$

$$\vdots$$

$$L_{i-1} = L_{min} \cdot \left(\eta_{i-1} - \sqrt{\eta_{i-1}^{2} - \eta_{i-1}}\right)$$

$$W_{i-1} = L_{min} \cdot \left(\eta_{i-1} - \sqrt{\eta_{i-1}^{2} - \eta_{i-1}}\right)$$

$$\vdots$$

$$L_{n} = L_{min} \cdot \left(\eta_{n} - \sqrt{\eta_{n}^{2} - \eta_{n}}\right)$$

$$W_{n} = L_{min} \cdot \left(\eta_{n} - \sqrt{\eta_{n}^{2} - \eta_{n}}\right)$$

Zur Gewährleistung einer einheitlichen Umgebung für jede Kapazität werden entsprechende Dummy-Strukturen erstellt. In der Abbildung 2-17 ist das fertige Layout für drei gepaarte Kapazitäten dargestellt. Zur Reduzierung der Folgen durch das Ätzen werden die Ecken der oberen Maskenebene der Kapazitäten mit 45° Abschrägungen versehen. Ferner erhält jede Kapazität, die nicht als Dummy-Struktur dient, einen mittig platzierten Kontakt zum Anschluss von Metall-Leitungen. Die Verdrahtungen der jeweiligen Kapazitäten werden kreuzungsfrei zum Rand des Moduls herausgeführt. Anschließend erfolgt die Konstruktion zweier Guardringe um das Kapazitätsfeld.

Abbildung 2-17: Automatisch erstelltes Layout von 3 gepaarten Kapazitäten

# 3 Operationsverstärker und Komparatoren

Ein Operationsverstärker besteht aus einer differentiellen Eingangsstufe, eventuell einer Zwischenstufe und einer Ausgangsstufe. Die Stufen sind häufig mittels einer Kompensation verbunden. Ebenso ist ein Bias-Netzwerk erforderlich. Ein großer Teil der integrierten Operationsverstärker wird für die SC-Schaltungstechnik eingesetzt. Weitere Einsatzgebiete stellen beispielsweise die gmC-Filter dar. Die erste Stufe eines Operationsverstärkers ist stets eine Differenzstufe. Falls die Anforderungen an die Verstärkung höher ausfallen bzw. andere Spezifikationsgrößen nicht eingehalten werden können, so müssen weitere Stufen eingebaut werden. Ein Überblick zum Design von Operationsverstärkern ist durch die Artikel in [Gray80], [Gray82], [Gray93] und [Lake94] gegeben.

Ein Komparator ist ein Operationsverstärker ohne Frequenzkompensation, weist jedoch eine ähnlich hohe Verstärkung auf. Infolge der fehlenden Kompensation ist ein rückgekoppelter Betrieb nicht möglich, sondern der Komparator darf nur offen zum Vergleich zweier Signale verwendet werden. Andernfalls besteht die Gefahr, dass die resultierende Schaltung instabil wird.

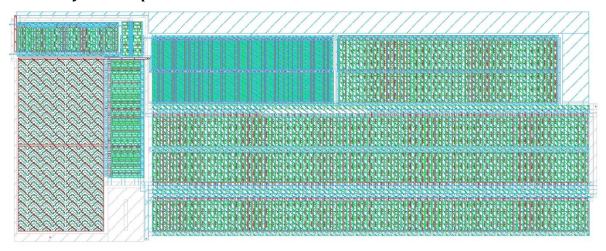

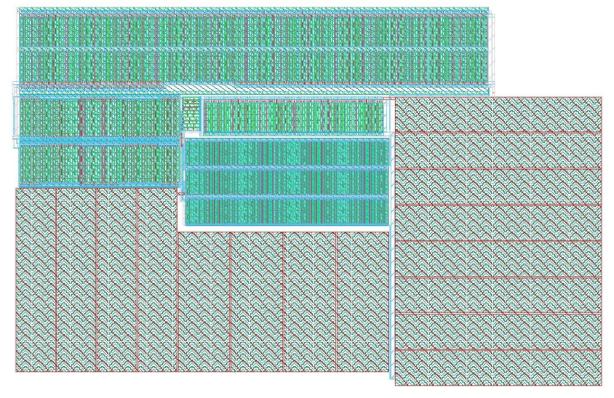

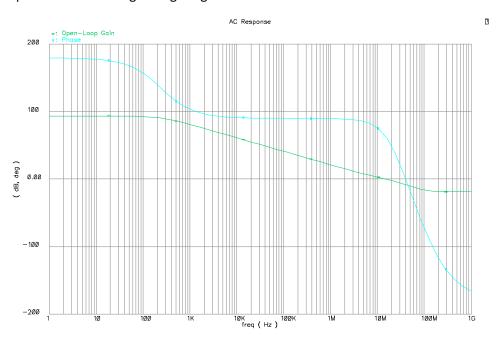

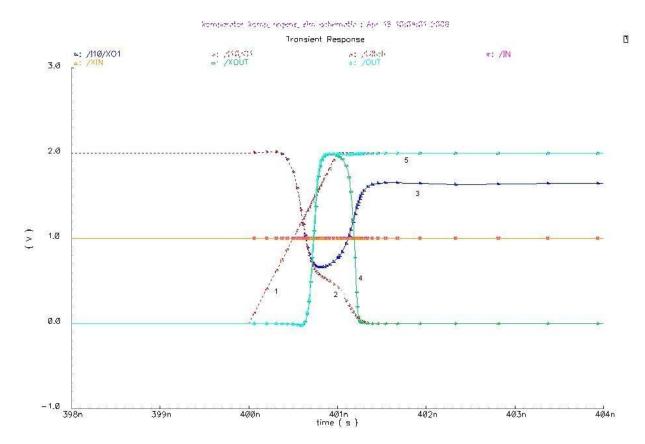

In diesem Kapitel werden die im Rahmen der vorliegenden Arbeit entworfenen integrierten Schaltungen näher beschrieben. Das Layout der Zellen der Verstärker und der Komparatoren wurde mit Hilfe der Modulgeneratorumgebung erstellt, wobei die Module in MOGLAN beschrieben sind. Es sind für einige der vorgestellten Operationsverstärker Prototypen in einer 0.25µm CMOS Technologie der IHP GmbH angefertigt worden. Die Messergebnisse dieser Schaltungen werden in diesem Kapitel ebenfalls präsentiert.

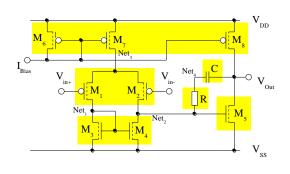

# 3.1 Zweistufige Operationsverstärker

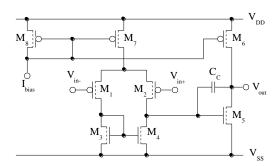

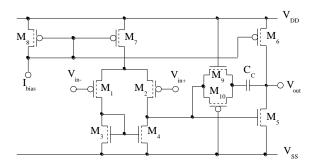

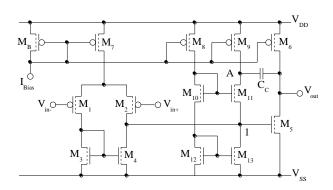

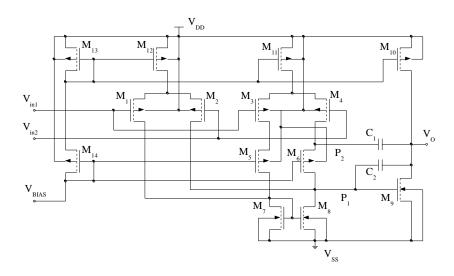

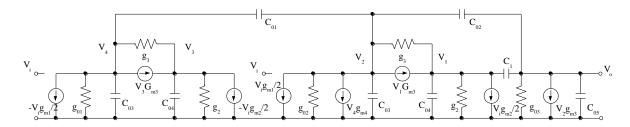

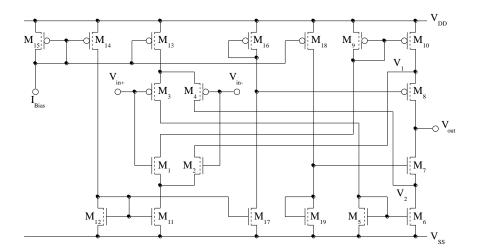

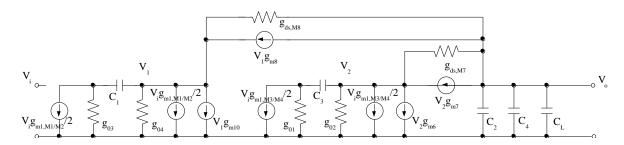

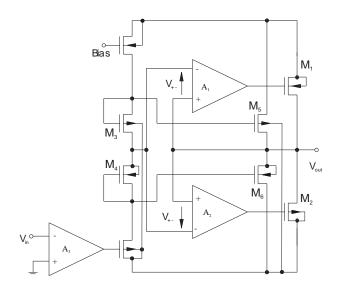

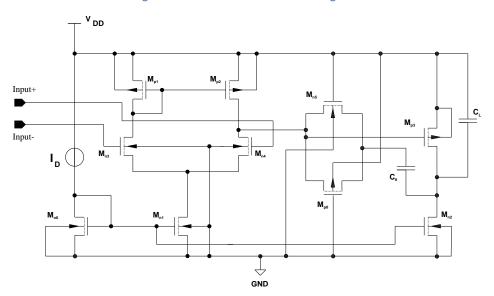

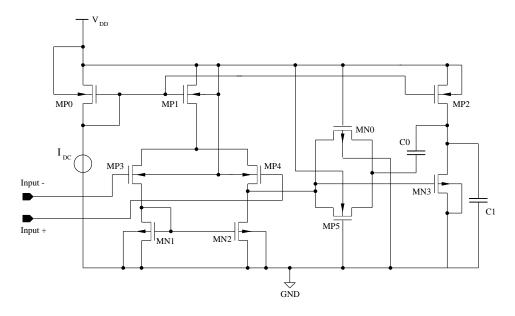

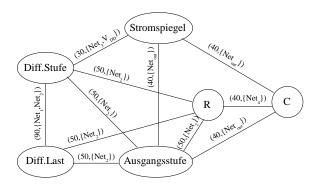

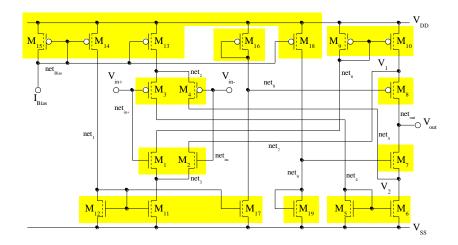

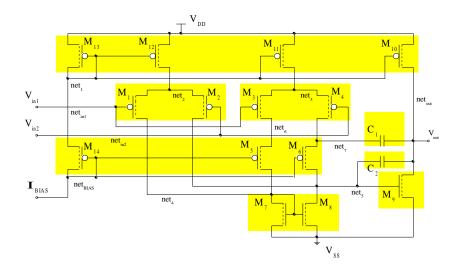

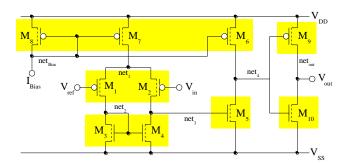

Ein zweistufiger Verstärker setzt sich grundlegend aus einer Differenzstufe und einer Inverterstufe zusammen. Anhand der Schaltung in Abbildung 3-1 kann die generelle Funktionsweise eines zweistufigen CMOS-Operationsverstärkers verdeutlicht werden.

Abbildung 3-1: Zweistufiger CMOS-Operationsverstärker

Die beiden Transistoren  $M_1$  und  $M_2$  bilden mit dem Stromquellentransistor M7 eine Differenzstufe, deren Drainströme durch den Stromspiegel  $M_3$  und  $M_4$  den zweiten Verstärkertransistor  $M_5$  ansteuern. Die Ausgangsspannung greift man ohne spezielle Endstufe am Arbeitswiderstand des Transistors  $M_5$ , nämlich dem Stromquellentransistor  $M_6$ , ab. Aus Symmetriegründen sind für die beiden Differenzverstärkertransistoren  $M_1$ ,  $M_2$  sowie für die Stromspiegeltransistoren  $M_3$ ,  $M_4$  jeweils identische Dimensionierungen zu wählen. Damit sich im Ruhezustand für  $V_{in-}$  =  $V_{in+}$  =  $V_{B/2}$  auch  $V_{out}$  =  $V_{B/2}$  einstellt, müssen die Drain-Ströme der Transistoren  $M_5$  und  $M_6$  gleich sein. Die

Leerlaufverstärkung ist mit einem geringen Aufwand durch eine Multiplikation der Einzelverstärkungen der beiden Stufen hinreichend genau anzugeben:

$$\frac{V_o}{V_i}(0) \approx \frac{g_{m1}}{g_{ds2} + g_{ds4}} \cdot \frac{g_{m5}}{g_{ds5} + g_{ds6}}.$$

(3-1)

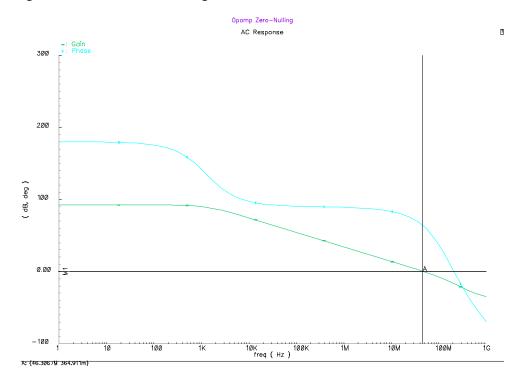

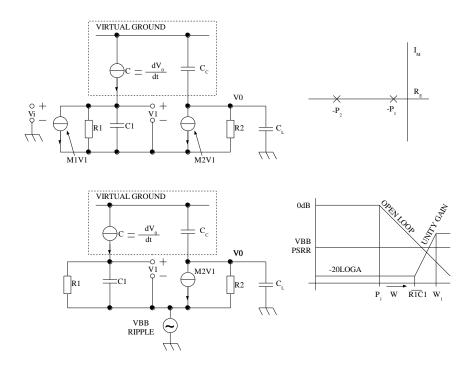

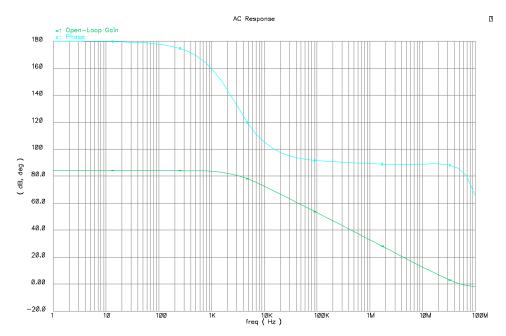

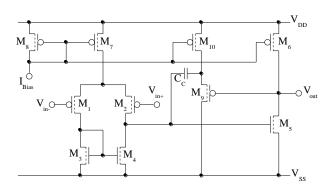

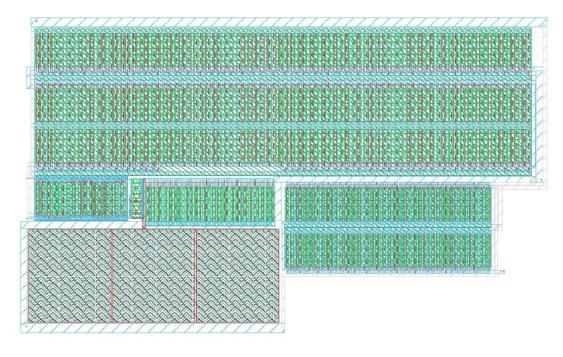

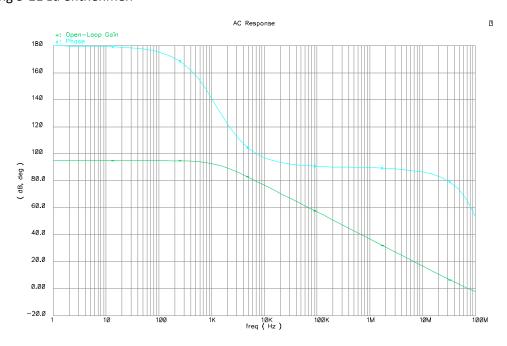

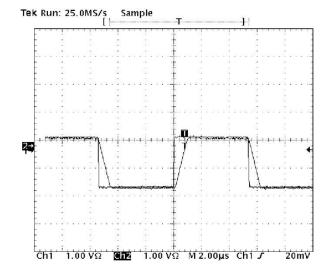

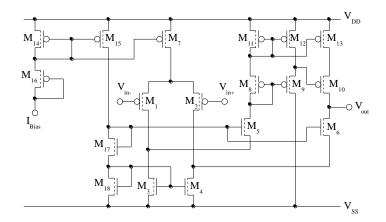

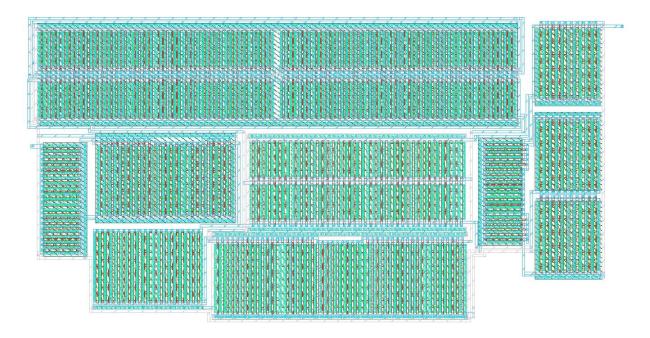

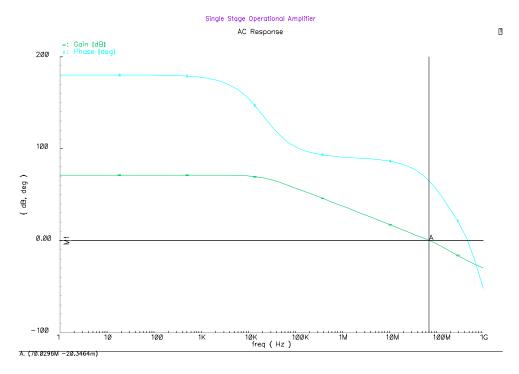

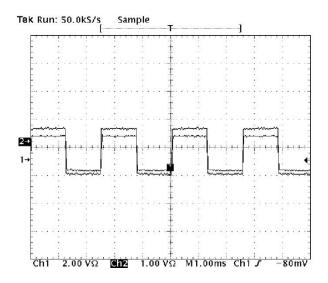

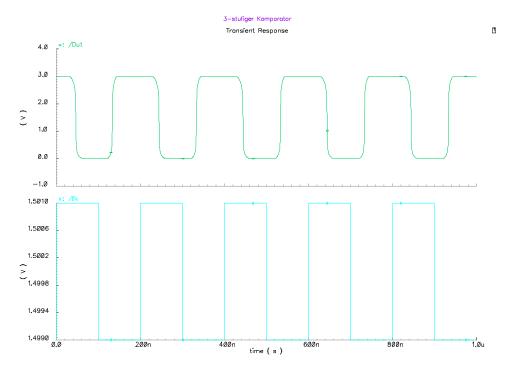

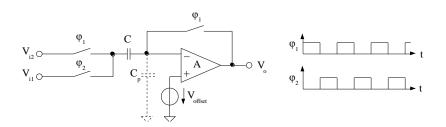

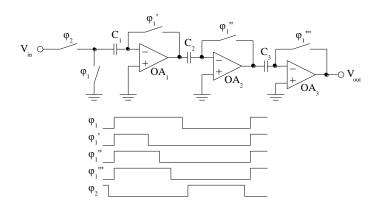

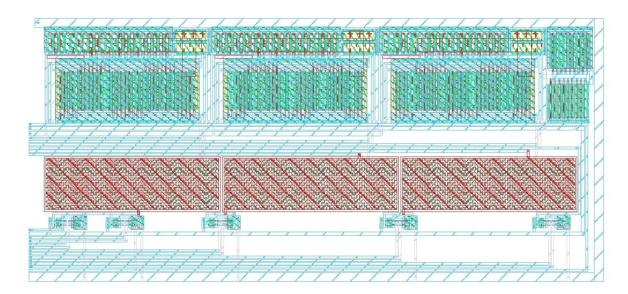

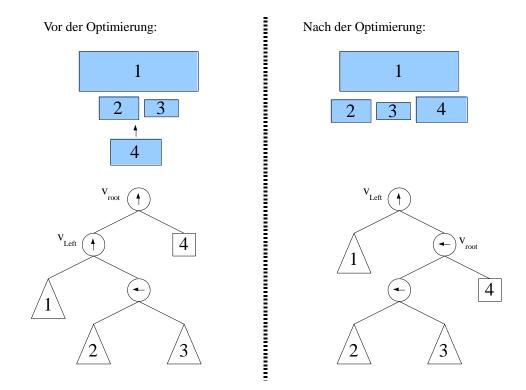

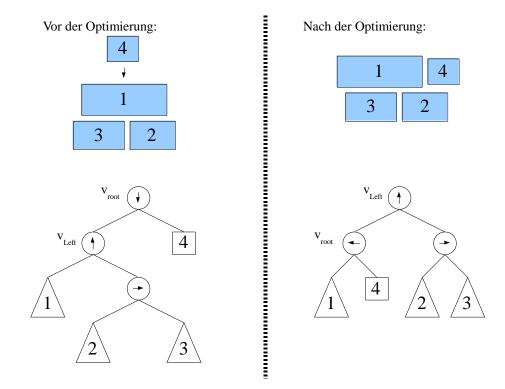

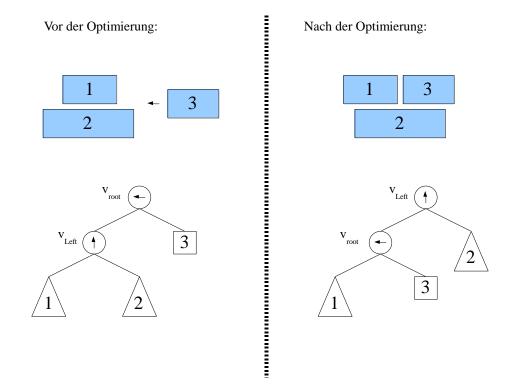

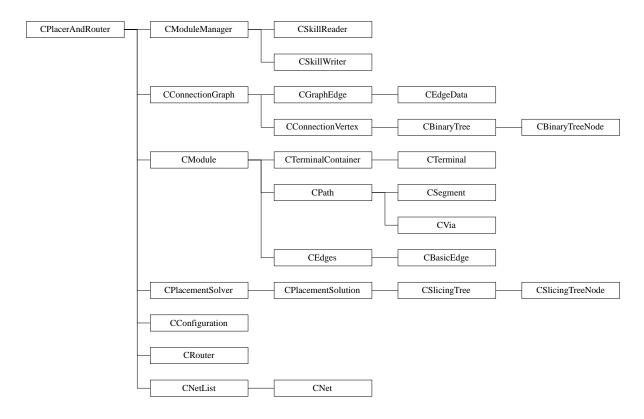

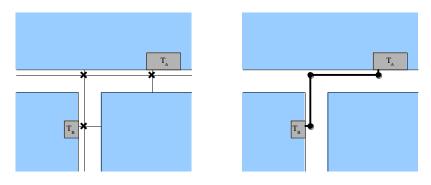

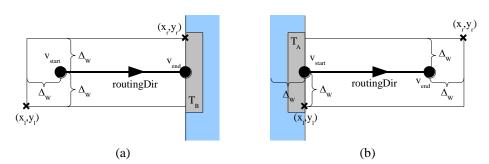

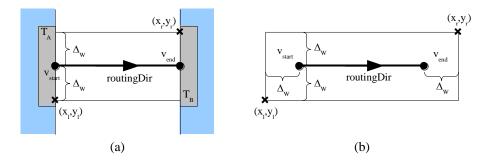

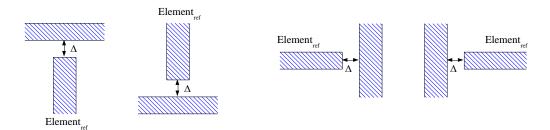

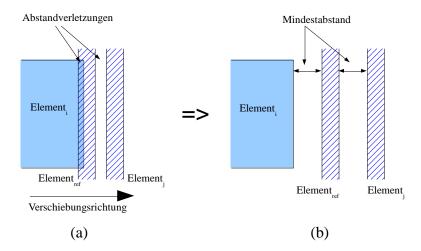

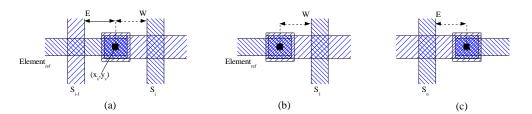

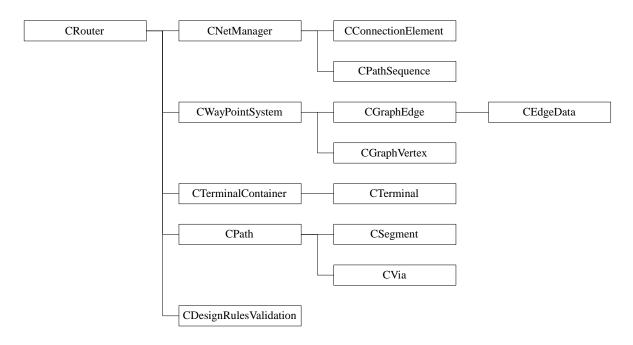

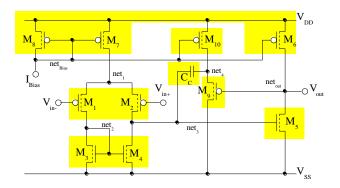

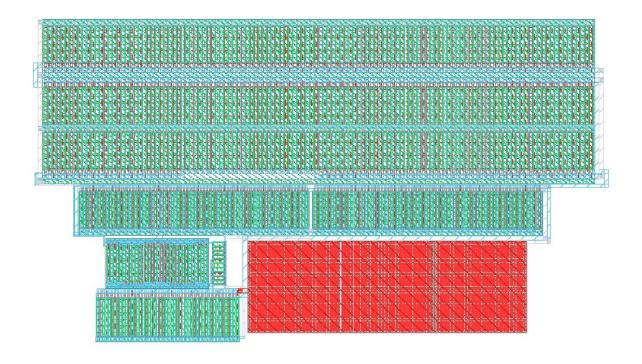

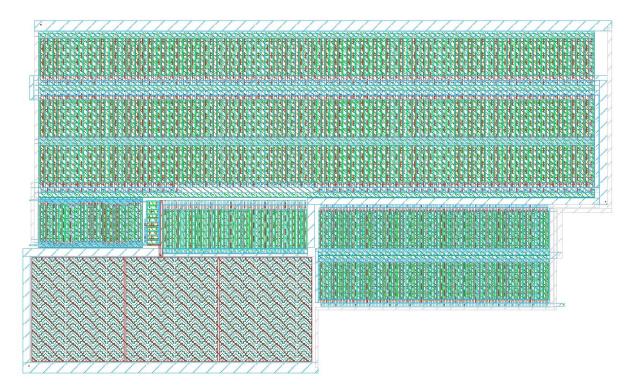

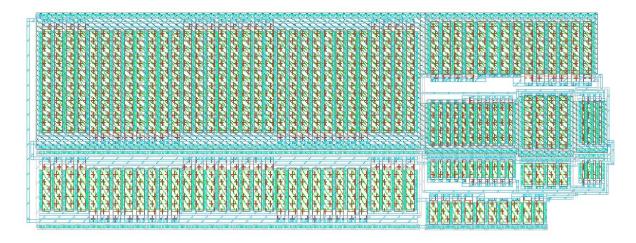

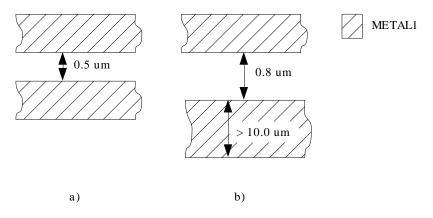

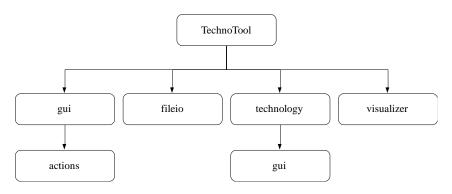

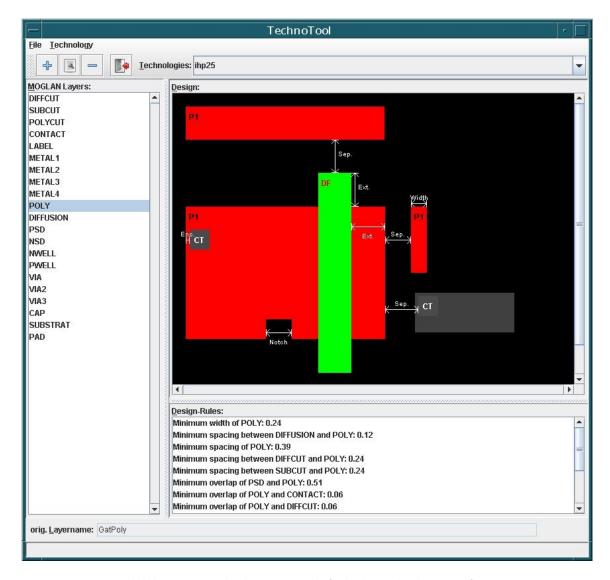

Insgesamt weist die Übertragungsfunktion für eine solche Struktur zwei Polstellen auf. Eine Stabilität kann nur dann gewährleistet werden, wenn der Frequenzabstand zwischen den beiden Polen hinreichend groß ist. Bei einem zweistufigen Verstärker liegen die beiden Polstellen jedoch relativ dicht beieinander, so dass die Einführung einer Kompensation notwendig ist [Malo01]. Hierbei wird eine Kompensationskapazität zwischen dem Eingang und dem Ausgang der zweiten Stufe eingefügt.